### **Integrated Driver** and MOSFET

#### Description

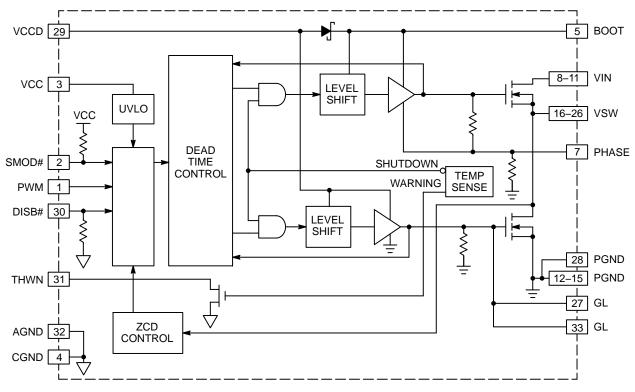

The NCP302040 integrates a MOSFET driver, high-side MOSFET and low-side MOSFET into a single package.

The driver and MOSFETs have been optimized for high-current DC-DC buck power conversion applications. The NCP302040 integrated solution greatly reduces package parasitics and board space compared to a discrete component solution.

#### Features

- Capable of Average Currents up to 40 A

- Capable of Switching at Frequencies up to 2 MHz

- Capable of Peak Currents up to 75 A

- Compatible with 3.3 V or 5 V PWM Input

- Responds Properly to 3-level PWM Inputs

- Option for Zero Cross Detection with 3-level PWM

- Internal Bootstrap Diode

- Undervoltage Lockout

- Supports Intel<sup>®</sup> Power State 4

- Thermal Warning output

- Thermal Shutdown

#### Applications

Desktop & Notebook Microprocessors

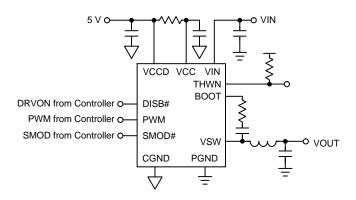

**Figure 1. Application Schematic**

#### **ON Semiconductor®**

www.onsemi.com

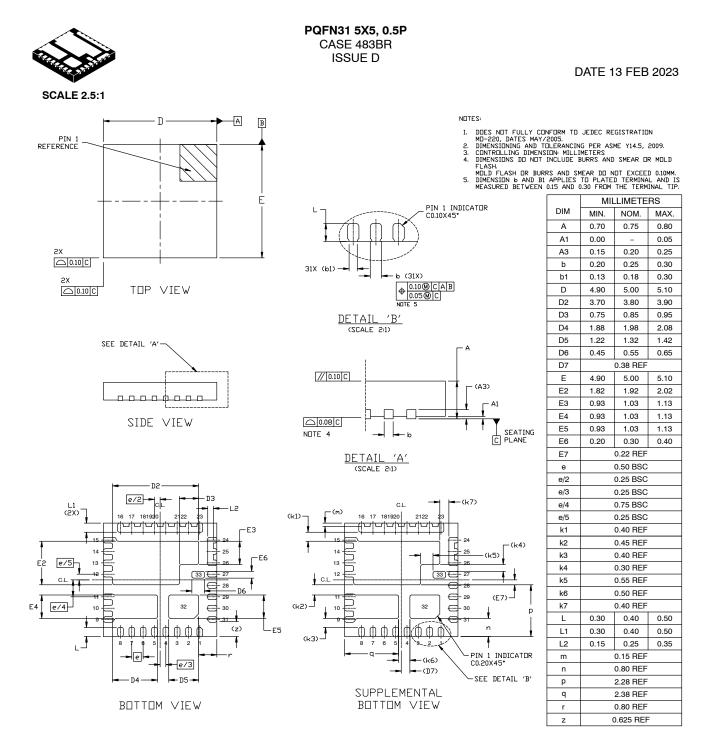

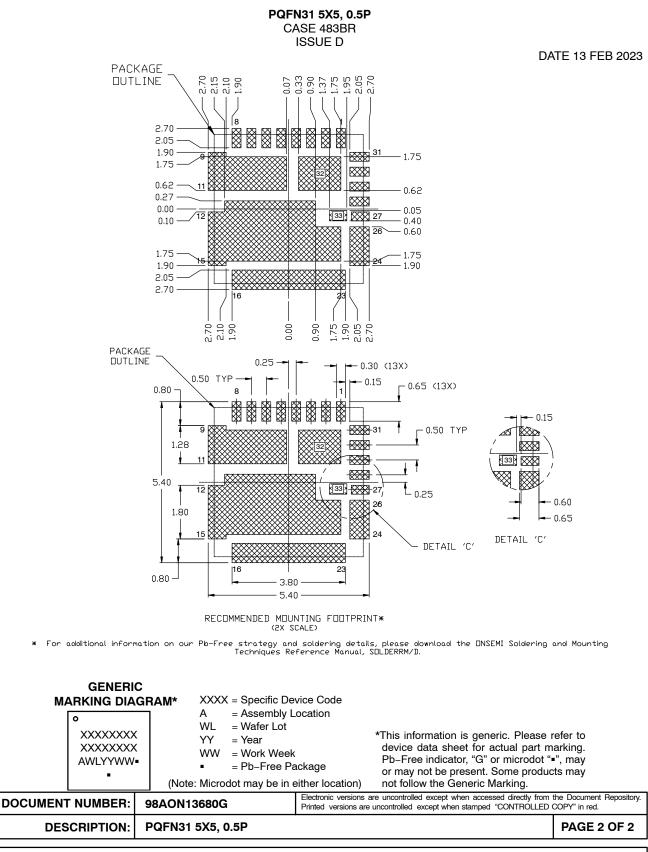

PQFN31 5x5. 0.5P Case 483BR

#### MARKING DIAGRAM

WW = Work Week

А

#### ORDERING INFORMATION

| Device         | Package             | Shipping <sup>†</sup> |

|----------------|---------------------|-----------------------|

| NCP302040MNTWG | PQFN31<br>(Pb–Free) | 3000 /<br>Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

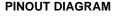

#### Table 1. PIN LIST AND DESCRIPTIONS

| Pin No.   | Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | PWM        | PWM Control Input and Zero Current Detection Enable                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2         | SMOD#      | <ul> <li>Skip Mode pin. 3-state input (see Table 1 LOGIC TABLE):</li> <li>SMOD# = High → State of PWM determine whether the NCP302040 performs ZCD or not.</li> <li>SMOD# = Mid → Connects PWM to internal resistor divider placing a bias voltage on PWM pin. Otherwise, logic is equivalent to SMOD# in the high state.</li> <li>SMOD# = Low → Placing PWM into mid-state pulls GH and GL low without delay. There is an internal pull-up resistor to VCC on this pin.</li> </ul> |

| 3         | VCC        | Control Power Supply Input                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4, 32     | CGND, AGND | Signal Ground (pin 4 and pad 32 are internally connected)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5         | BOOT       | Bootstrap Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6         | nc         | Open pin (not used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7         | PHASE      | Bootstrap Capacitor Return                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8–11      | VIN        | Conversion Supply Power Input                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12–15, 28 | PGND       | Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16–26     | VSW        | Switch Node Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 27, 33    | GL         | Low Side FET Gate Access (pin 27 and pad 33 are internally connected)                                                                                                                                                                                                                                                                                                                                                                                                               |

| 29        | VCCD       | Driver Power Supply Input                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 30        | DISB#      | Output disable pin. When this pin is pulled to a logic high level, the driver is enabled. There is an internal pull-down resistor on this pin.                                                                                                                                                                                                                                                                                                                                      |

| 31        | THWN       | Thermal warning indicator. This is an open-drain output. When the temperature at the driver die reaches $T_{THWN}$ , this pin is pulled low.                                                                                                                                                                                                                                                                                                                                        |

#### Table 2. ABSOLUTE MAXIMUM RATINGS (Electrical Information – all signals referenced to PGND unless noted otherwise)

| Pin Name/Parameter  | Min  | Max                    | Unit |

|---------------------|------|------------------------|------|

| VCC, VCCD           | -0.3 | 6.5                    | V    |

| VIN                 | -0.3 | 30                     | V    |

| BOOT (DC)           | -0.3 | 35                     | V    |

| BOOT (< 20 ns)      | -0.3 | 40                     | V    |

| BOOT to PHASE (DC)  | -0.3 | 6.5                    | V    |

| VSW, PHASE (DC)     | -0.3 | 30                     | V    |

| VSW, PHASE (< 5 ns) | -5   | 37                     | V    |

| All Other Pins      | -0.3 | V <sub>VCC</sub> + 0.3 | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **Table 3. THERMAL INFORMATION**

| Rating                                               | Symbol           | Value       | Unit |

|------------------------------------------------------|------------------|-------------|------|

| Thermal Resistance (under On Semi SPS Thermal Board) | $\theta_{JA}$    | 12.4        | °C/W |

|                                                      | $\theta_{J-PCB}$ | 1.8         | °C/W |

| Operating Junction Temperature Range (Note 1)        | TJ               | -40 to +150 | °C   |

| Operating Ambient Temperature Range                  | T <sub>A</sub>   | -40 to +125 | °C   |

| Maximum Storage Temperature Range                    | T <sub>STG</sub> | -55 to +150 | °C   |

| Maximum Power Dissipation                            |                  | 9.5         | W    |

| Moisture Sensitivity Level                           | MSL              | 1           |      |

1. The maximum package power dissipation must be observed.

JESD 51–5 (1S2P Direct-Attach Method) with 0 LFM

JESD 51–7 (1S2P Direct-Attach Method) with 0 LFM

#### Table 4. RECOMMENDED OPERATING CONDITIONS

| Parameter                 | Pin Name  | Conditions                                                                                              | Min | Тур | Max | Unit |

|---------------------------|-----------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Supply Voltage Range      | VCC, VCCD |                                                                                                         | 4.5 | 5.0 | 5.5 | V    |

| Conversion Voltage        | VIN       |                                                                                                         | 4.5 | 12  | 20  | V    |

| Continuous Output Current |           | $F_{SW}$ = 1 MHz, $V_{IN}$ = 12 V, $V_{OUT}$ = 1.0 V, $T_A$ = 25°C                                      | -   | I   | 35  | А    |

|                           |           | $F_{SW} = 300 \text{ kHz}, V_{IN} = 12 \text{ V}, V_{OUT} = 1.0 \text{ V}, T_A = 25^{\circ}\text{C}$    | -   | -   | 40  | А    |

| Peak Output Current       |           | $F_{SW}$ = 500 kHz, $V_{IN}$ = 12 V, $V_{OUT}$ = 1.0 V,<br>Duration = 10 ms, Period = 1 s, $T_A$ = 25°C | -   | -   | 70  | A    |

| Junction Temperature      |           |                                                                                                         | -40 | -   | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### Table 5. ELECTRICAL CHARACTERISTICS

$(V_{VCC} = V_{VCCD} = 5.0 \text{ V}, V_{VIN} = 12 \text{ V}, V_{DISB\#} = 2.0 \text{ V}, C_{VCCD} = C_{VCC} = 0.1 \mu\text{F}$  unless specified otherwise) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \le T_J \le 125^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.

| Parameter                        | Symbol                  | Conditions                                                          | Min  | Тур | Max | Unit |

|----------------------------------|-------------------------|---------------------------------------------------------------------|------|-----|-----|------|

| VCC SUPPLY CURRENT               |                         |                                                                     |      |     |     | •    |

| Operating                        |                         | DISB# = 5 V, PWM = 400 kHz                                          | -    | 1   | 2   | mA   |

| No switching                     |                         | DISB# = 5 V, PWM = 0 V                                              | -    | -   | 2   | mA   |

| Disabled                         |                         | DISB# = 0 V, SMOD# = VCC                                            | -    | 0.4 | 1   | μA   |

|                                  |                         | DISB# = 0 V, SMOD# = GND                                            | _    | 6   | 13  | μΑ   |

| UVLO Start Threshold             | V <sub>UVLO</sub>       | VCC Rising                                                          | 2.9  | -   | 3.3 | V    |

| UVLO Hysteresis                  |                         |                                                                     | 150  | -   | -   | mV   |

| CCD SUPPLY CURRENT               |                         |                                                                     |      | •   | •   | •    |

| Enabled, No Switching            |                         | DISB# = 5 V, PWM = 0 V, V <sub>PHASED</sub> = 0 V                   | -    | 175 | 300 | μΑ   |

| Disabled                         |                         | DISB# = 0 V                                                         | -    | 0.4 | 1   | μΑ   |

| Operating                        |                         | DISB# = 5 V, PWM = 400 kHz                                          | _    | -   | 20  | mA   |

| DISB# INPUT                      | •                       |                                                                     |      | •   | •   | •    |

| Input Resistance                 |                         | To Ground                                                           | -    | 467 | -   | kΩ   |

| Upper Threshold                  | V <sub>UPPER</sub>      |                                                                     | -    | -   | 2.0 | V    |

| Lower Threshold                  | V <sub>LOWER</sub>      |                                                                     | 0.8  | -   | -   | V    |

| Hysteresis                       |                         | V <sub>UPPER</sub> – V <sub>LOWER</sub>                             | 200  | -   | -   | mV   |

| Enable Delay Time                |                         | Time from DISB# transitioning HI to when VSW responds to PWM.       | -    | -   | 40  | μs   |

| Disable Delay Time               |                         | Time from DISB# transitioning LOW to when both output FETs are off. | -    | 21  | 50  | ns   |

| SMOD# INPUT                      |                         |                                                                     |      |     |     |      |

| SMOD# Input Voltage High         | V <sub>SMOD_HI</sub>    |                                                                     | 2.65 | -   | -   | V    |

| SMOD# Input Voltage Mid-state    | V <sub>SMOD#_MID</sub>  |                                                                     | 1.4  | -   | 2.0 | V    |

| SMOD# Input Voltage Low          | V <sub>SMOD_LO</sub>    |                                                                     | _    | -   | 0.7 | V    |

| SMOD# Input Resistance           | R <sub>SMOD#_UP</sub>   | Pull-up resistance to VCC                                           | -    | 455 | -   | kΩ   |

| SMOD# Propagation Delay, Falling | T <sub>SMOD#_PD_F</sub> | PWM = High-to-Low,<br>SMOD# = Low to GL = 90%                       | -    | 34  | 40  | ns   |

| SMOD# Propagation Delay, Rising  | T <sub>SMOD#_PD_R</sub> | PWM = High-to-Low,<br>SMOD# = High to GL = 10%                      | -    | 22  | 30  | ns   |

| PWM INPUT                        | J                       | 1                                                                   |      | 1   | 1   | 1    |

| Input High Voltage               | V <sub>PWM_HI</sub>     |                                                                     | 2.65 | -   | -   | V    |

| Input Mid-state Voltage          |                         |                                                                     | 1.4  | _   | 2.0 | V    |

|                         | I                    |                                          |     |   |     |    |

|-------------------------|----------------------|------------------------------------------|-----|---|-----|----|

| Input Mid-state Voltage | V <sub>PWM_MID</sub> |                                          | 1.4 | - | 2.0 | V  |

| Input Low Voltage       | V <sub>PWM_LO</sub>  |                                          | 1   | 1 | 0.7 | V  |

| Input Resistance        | R <sub>PWM_HIZ</sub> | SMOD# = $V_{SMOD#_HI}$ or $V_{SMOD#_LO}$ | 10  | I | -   | MΩ |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### Table 5. ELECTRICAL CHARACTERISTICS (continued)

$(V_{VCC} = V_{VCCD} = 5.0 \text{ V}, V_{VIN} = 12 \text{ V}, V_{DISB\#} = 2.0 \text{ V}, C_{VCCD} = C_{VCC} = 0.1 \mu\text{F}$  unless specified otherwise) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \le T_J \le 125^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.

| Parameter Symb                                          |                         | Conditions                                  | Min      | Тур | Max      | Unit |

|---------------------------------------------------------|-------------------------|---------------------------------------------|----------|-----|----------|------|

| PWM INPUT                                               |                         |                                             |          |     |          |      |

| Input Resistance                                        | R <sub>PWM_BIAS</sub>   | SMOD# = V <sub>SMOD#_MID</sub>              | _        | 68  | -        | kΩ   |

| PWM Input Bias Voltage                                  | V <sub>PWM_BIAS</sub>   | SMOD# = V <sub>SMOD#_MID</sub>              | _        | 1.7 | -        | V    |

| Non-overlap Delay, Leading Edge                         | T <sub>NOL_L</sub>      | GL Falling = 1 V to<br>GH–VSW Rising = 1 V  | -        | 13  | -        | ns   |

| Non-overlap Delay, Trailing Edge                        | T <sub>NOL_T</sub>      | GH–VSW Falling = 1 V to<br>GL Rising = 1 V  | -        | 12  | -        | ns   |

| PWM Propagation Delay, Rising                           | T <sub>PWM,PD_R</sub>   | PWM = High to GL = 90%                      | -        | 13  | 35       | ns   |

| PWM Propagation Delay, Falling                          | T <sub>PWM,PD_F</sub>   | PWM = Low to VSW = 90%                      | -        | 47  | 52       | ns   |

| Exiting PWM Mid-state Propagation<br>Delay, Mid-to-Low  | T <sub>PWM_EXIT_L</sub> | PWM = Mid-to-Low to GL = 10%                | -        | 14  | 25       | ns   |

| Exiting PWM Mid-state Propagation<br>Delay, Mid-to-High | T <sub>PWM_EXIT_H</sub> | PWM = Mid-to-High to VSW = 10%              | -        | 13  | 25       | ns   |

| ZCD FUNCTION                                            |                         |                                             |          |     |          |      |

| Zero Cross Detect Threshold                             | V <sub>ZCD</sub>        |                                             | -        | -6  | _        | mV   |

| ZCD Blanking + Debounce Time                            | t <sub>BLNK</sub>       |                                             | _        | 330 | -        | ns   |

| THERMAL WARNING & SHUTDOWN                              | 4                       |                                             | -        |     | 1        |      |

| Thermal Warning Temperature                             | T <sub>THWN</sub>       | Temperature at Driver Die                   | -        | 150 | -        | °C   |

| Thermal Warning Hysteresis                              | T <sub>THWN_HYS</sub>   |                                             | -        | 15  | _        | °C   |

| Thermal Shutdown Temperature                            | T <sub>THDN</sub>       | Temperature at Driver Die                   | -        | 180 | _        | °C   |

| Thermal Shutdown Hysteresis                             | T <sub>THDN_HYS</sub>   |                                             | -        | 25  | -        | °C   |

| THWN Open Drain Current                                 | I <sub>THWN</sub>       |                                             | _        | _   | 5        | mA   |

| BOOSTSTRAP DIODE                                        |                         | L                                           |          |     |          |      |

| Forward Voltage                                         |                         | Forward Bias Current = 2.0 mA               | _        | 380 | _        | mV   |

| HIGH-SIDE DRIVER                                        | ļ                       | ł                                           | <b>ļ</b> | ļ   | <u> </u> | ļ    |

| Output Impedance, Sourcing                              | R <sub>SOURCE_GH</sub>  | Source Current = 100 mA                     | _        | 0.9 | _        | Ω    |

| Output Sourcing Peak Current                            | I <sub>SOURCE_GH</sub>  |                                             | _        | 2   | _        | Α    |

| Output Impedance, Sinking                               | R <sub>SINK_GH</sub>    | Source Current = 100 mA                     | _        | 0.7 | _        | Ω    |

| Output Sinking Peak Current                             | I <sub>SINK_GH</sub>    |                                             | _        | 2.5 | _        | Α    |

| LOW-SIDE DRIVER                                         |                         |                                             | 1        | 1   |          | 1    |

| Output Impedance, Sourcing                              | R <sub>SOURCE_GL</sub>  | Source Current = 100 mA                     | -        | 0.9 | -        | Ω    |

| Output Sourcing Peak Current                            | I <sub>SOURCE_GL</sub>  | GL = 2.5 V                                  | _        | 2   | _        | Α    |

| Output Impedance, Sinking                               | R <sub>SINK_GH</sub>    | Sink Current = 100 mA                       | _        | 0.4 | -        | Ω    |

| Output Sinking Peak Current                             | I <sub>SINK_GL</sub>    | GL = 2.5 V                                  | _        | 4.5 | -        | А    |

| GL Rise Time                                            | T <sub>R_GL</sub>       | GL = 10% to 90%, C <sub>LOAD</sub> = 3.0 nF | _        | 12  | -        | ns   |

| GL Fall Time                                            | T <sub>F_GL</sub>       | GL = 90% to 10%, C <sub>LOAD</sub> = 3.0 nF | _        | 6   | _        | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### Table 6. LOGIC TABLE

| INPUT TRUTH TABLE |     |          |   |              |  |  |

|-------------------|-----|----------|---|--------------|--|--|

| DISB#             | PWM | GL       |   |              |  |  |

| L                 | Х   | X        | L | L            |  |  |

| Н                 | Н   | X        | н | L            |  |  |

| Н                 | L   | X        | L | Н            |  |  |

| Н                 | MID | H or MID | L | ZCD (Note 5) |  |  |

| н                 | MID | L        | L | L (Note 6)   |  |  |

PWM input is driven to mid-state with internal divider resistors when SMOD# is driven to mid-state and PWM input is undriven externally.

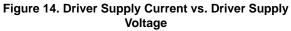

GL goes low following 80 ns de-bounce time, 250 ns blanking time and then SW exceeding ZCD threshold.

There is no delay before GL goes low.

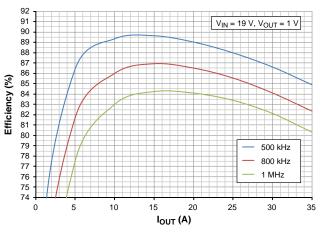

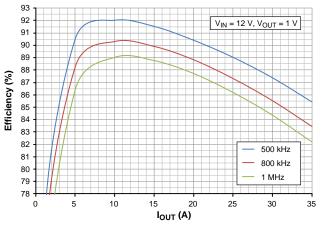

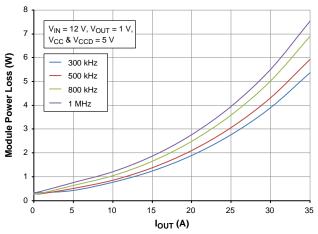

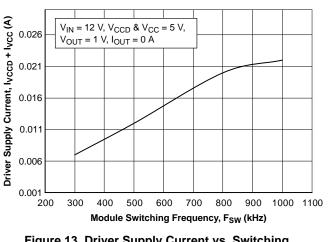

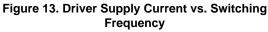

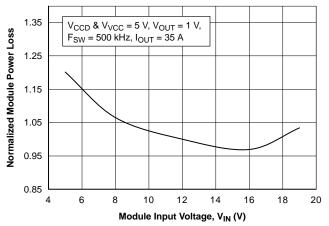

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

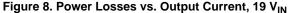

(Test Conditions:  $V_{IN} = 12 \text{ V}$ ,  $V_{CC} = PV_{CC} = 5 \text{ V}$ ,  $V_{OUT} = 1 \text{ V}$ ,  $L_{OUT} = 250 \text{ nH}$ ,  $T_A = 25^{\circ}C$  and natural convection cooling, unless otherwise noted.)

Figure 3. Efficiency – 19 V Input, 1.0 V Output

Figure 5. Efficiency – 12 V Input, 1.0 V Output

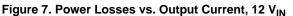

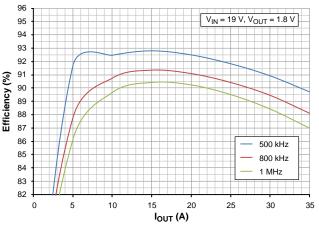

Figure 4. Efficiency – 19 V Input, 1.8 V Output

Figure 6. Efficiency – 12 V Input, 1.8 V Output

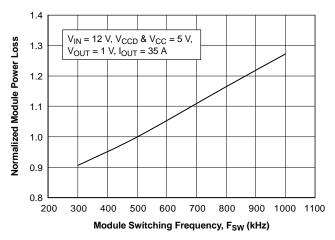

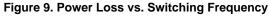

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

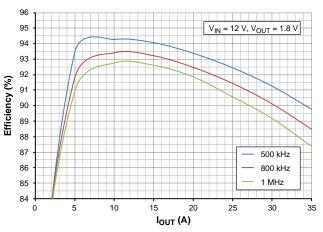

(Test Conditions:  $V_{IN}$  = 12 V,  $V_{CC}$  =  $PV_{CC}$  = 5 V,  $V_{OUT}$  = 1 V,  $L_{OUT}$  = 250 nH,  $T_A$  = 25°C and natural convection cooling, unless otherwise noted.)

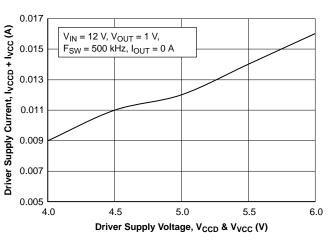

Figure 11. Power Loss vs. Driver Supply Voltage

Figure 10. Power Loss vs. Input Voltage

Figure 12. Power Loss vs. Output Voltage

#### **APPLICATIONS INFORMATION**

#### Theory of Operation

The NCP302040 is an integrated driver and MOSFET module designed for use in a synchronous buck converter topology. The NCP302040 supports numerous application control definitions including ZCD (Zero Current Detect) and alternately PWM Tristate control. A PWM input signal is required to control the drive signals to the high-side and low-side integrated MOSFETs.

#### Low-Side Driver

The low-side driver drives an internal, ground-referenced low- $R_{DS}(on)$  N-Channel MOSFET. The voltage supply for the low-side driver is internally connected to the VCCD and PGND pins.

#### **High-Side Driver**

The high-side driver drives an internal, floating low- $R_{DS}(on)$  N-channel MOSFET. The gate voltage for the high side driver is developed by a bootstrap circuit referenced to Switch Node (VSW and PHASE) pins.

The bootstrap circuit is comprised of the integrated diode and an external bootstrap capacitor and resistor. When the NCP302040 is starting up, the VSW pin is at ground, allowing the bootstrap capacitor to charge up to VCCD through the bootstrap diode (see Figure 1). When the PWM input is driven high, the high-side driver turns on the high-side MOSFET using the stored charge of the bootstrap capacitor. As the high-side MOSFET turns on, the voltage at the VSW and PHASE pins rises. When the high-side MOSFET is fully turned on, the switch node settles to VIN and the BST pin settles to VIN + VCCD (excluding parasitic ringing).

#### **Bootstrap Circuit**

The bootstrap circuit relies on an external charge storage capacitor ( $C_{BST}$ ) and an integrated diode to provide current to the HS Driver. A multi-layer ceramic capacitor (MLCC) with a value greater than 100 nF should be used as the

bootstrap capacitor. An optional 1 to 4  $\Omega$  resistor in series with the bootstrap capacitor decreases the VSW overshoot.

#### **Power Supply Decoupling**

The NCP302040 sources relatively large currents into the MOSFET gates. In order to maintain a constant and stable supply voltage (VCCD) a low-ESR capacitor should be placed near the power and ground pins. A multi-layer ceramic capacitor (MLCC) between 1  $\mu$ F and 4.7  $\mu$ F is typically used.

A separate supply pin (VCC) is used to power the analog and digital circuits within the driver. A 1  $\mu$ F ceramic capacitor should be placed on this pin in close proximity to the NCP302040. It is good practice to separate the VCC and VCCD decoupling capacitors with a resistor (10  $\Omega$  typical) to avoid coupling driver noise to the analog and digital circuits that control the driver function (see Figure 1).

#### Safety Timer and Overlap Protection Circuit

It is important to avoid cross-conduction of the two MOSFETS which could result in a decrease in the power conversion efficiency or damage to the device.

The NCP302040 prevents cross-conduction by monitoring the status of the MOSFETs and applying the appropriate amount of non-overlap (NOL) time (the time between the turn-off of one MOSFET and the turn-on of the other MOSFET). When the PWM input pin is driven high, the gate of the low-side MOSFET (LSGATE) goes low after a propagation delay (tpdlGL). The time it takes for the low-side MOSFET to turn off is dependent on the total charge on the low-side MOSFET gate.

The NCP302040 monitors the gate voltage of both MOSFETs and the switch node voltage to determine the conduction status of the MOSFETs. Once the low-side MOSFET is turned off an internal timer delays (tpdhGH) the turn-on of the high-side MOSFET. When the PWM input pin goes low, the gate of the high-side MOSFET (HSGATE) goes low after the propagation delay (tpdlGH). The time to turn off the high-side MOSFET (tfGH) is dependent on the total gate charge of the high-side MOSFET. A timer is triggered once the high-side MOSFET stops conducting, to delay (tpdhGL) the turn-on of the low-side MOSFET.

#### Zero Current Detect

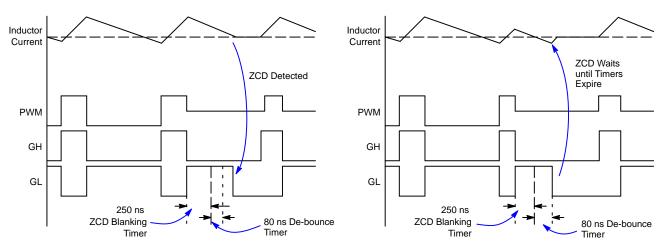

The Zero Current Detect PWM (ZCD\_PWM) mode is enabled when SMOD# is high (see Tables 6 and 8).

With PWM set to > VPWM\_HI, GL goes low and GH goes high after the non-overlap delay. When PWM is driven to < VPWM\_HI and to > VPWM\_LO, GL goes high after the non-overlap delay, and stays high for the duration of the ZCD blanking timer ( $T_{ZCD_BLANK}$ ) and an 80 ns de-bounce timer. Once this timer expires, VSW is monitored for zero current detection, and GL is pulled low once zero current is detected. The threshold on VSW to determine zero current undergoes an auto-calibration cycle every time DISB# is brought from low to high. This auto-calibration cycle typically takes 25 µs to complete.

#### **PWM** Input

The PWM Input pin is a tri-state input used to control the HS MOSFET ON/OFF state. It also determines the state of the LS MOSFET. See Table 6 for logic operation. The PWM in some cases must operate with frequency programming resistances to ground. These resistances can range from 10 k $\Omega$  to 300 k $\Omega$  depending on the application. When SMOD# is set to > VSMOD#\_HI or to < VSMOD#\_LO, the input impedance to the PWM input is very high in order to avoid interferences with controllers that must use programming resistances on the PWM pin.

If SMOD# is set to < VSMOD#\_HI and > VSMOD#\_LO (Mid-State), the PWM pin undriven default voltage is set to Mid-State with internal divider resistances.

#### Disable Input (DISB#)

The DISB# pin is used to disable the GH to the High-Side FET to prevent power transfer. The pin has a pull-down resistance to force a disabled state when it is left unconnected. DISB# can be driven from the output of a logic device or set high with a pull-up resistance to VCC.

#### VCC Undervoltage Lockout

The VCC pin is monitored by an Undervoltage Lockout Circuit (UVLO). VCC voltage above the rising threshold enables the NCP302040.

#### Table 7. UVLO/DISB# LOGIC TABLE

| UVLO | DISB# | Driver State           |

|------|-------|------------------------|

| L    | Х     | Disabled (GH = GL = 0) |

| Н    | L     | Disabled (GH = GL = 0) |

| Н    | Н     | Enabled (See Table 6)  |

| Н    | Open  | Disabled (GH = GL = 0) |

#### Thermal Warning/Thermal Shutdown Output

The THWN pin is an open drain output. When the temperature of the driver exceeds  $T_{THWN}$ , the THWN pin is pulled low indicating a thermal warning. At this point, the part continues to function normally. When the temperature drops  $T_{THWN}_{HYS}$  below  $T_{THWN}$ , the THWN pin goes high. If the driver temperature exceeds  $T_{THDN}$ , the part enters thermal shutdown and turns off both MOSFETs. Once the temperature falls  $T_{THDN}_{HYS}$  below  $T_{THDN}$ , the part resumes normal operation.

#### Skip Mode Input (SMOD#)

The SMOD# tri-state input pin has an internal pull-up resistance to VCC. When driven low, the SMOD# pin enables the low side synchronous MOSFET to operate independently of the internal ZCD function. When the SMOD# pin is set low while PWM is in the mid-state, the low side MOSFET is disabled to allow discontinuous mode operation.

The NCP302040 has the capability of internally connecting a resistor divider to the PWM pin. To engage this mode, SMOD# needs to be placed into mid-state. While in SMOD# mid-state, the IC logic is equivalent to SMOD# being in the high state.

NOTES: If the Zero Current Detect circuit detects zero current after the ZCD Wait timer period, the GL is driven low by the Zero Current Detect signal.

If the Zero Current Detect circuit detects zero current before the ZCD Wait timer period expires, the Zero Current detect signal is ignored and the GL is driven low at the end of the ZCD Wait timer period.

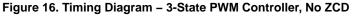

#### Figure 15. PWM Timing Diagram

For Use with Controllers with 3-State PWM and No Zero Current Detection Capability:

| PWM | SMOD# | GH (Not a Pin) | GL  |

|-----|-------|----------------|-----|

| Н   | Н     | ON             | OFF |

| М   | Н     | OFF            | ZCD |

| L   | Н     | OFF            | ON  |

This section describes operation with controllers that are capable of 3 states in their PWM output and relies on the NCP302040 to conduct zero current detection during discontinuous conduction mode (DCM).

The SMOD# pin needs to either be set to 5 V or left disconnected. The NCP302040 has an internal pull-up resistor that connects to VCC that sets SMOD# to the logic high state if this pin is disconnected.

To operate the buck converter in continuous conduction mode (CCM), PWM needs to switch between the logic high

and low states. To enter into DCM, PWM needs to be switched to the mid-state.

Whenever PWM transitions to mid-state, GH turns off and GL turns on. GL stays on for the duration of the de-bounce timer and ZCD blanking timers. Once these timers expire, the NCP302040 monitors the VSW voltage and turns GL off when VSW exceeds the ZCD threshold voltage. By turning off the LS FET, the body diode of the LS FET allows any positive current to go to zero but prevents negative current from conducting.

For Use with Controllers with 3-state PWM and Zero Current Detection Capability:

| PWM | SMOD# | GH (Not a Pin) | GL  |

|-----|-------|----------------|-----|

| Н   | L     | ON             | OFF |

| М   | L     | OFF            | OFF |

| L   | L     | OFF            | ON  |

| Table 9. LOGIC TABLE – | <b>3-STATE PWM CONTROLLERS WITH Z</b> | CD |

|------------------------|---------------------------------------|----|

|------------------------|---------------------------------------|----|

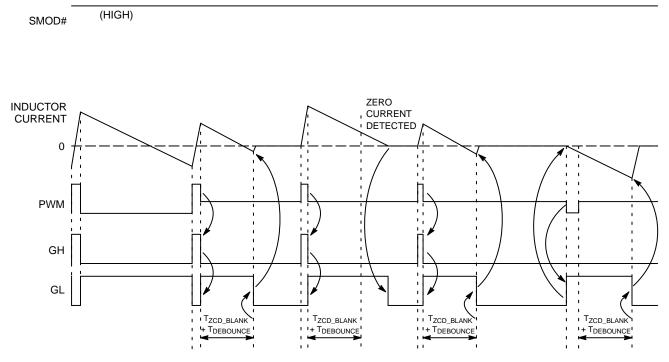

This section describes operation with controllers that are capable of 3 PWM output levels and have zero current detection during discontinuous conduction mode (DCM).

The SMOD# pin needs to be pulled low (below  $V_{SMOD\#\_LO}).$

To operate the buck converter in continuous conduction mode (CCM), PWM needs to switch between the logic high

and low states. During DCM, the controller is responsible for detecting when zero current has occurred, and then notifying the NCP302040 to turn off the LS FET. When the controller detects zero current, it needs to set PWM to mid-state, which causes the NCP302040 to pull both GH and GL to their off states without delay.

Figure 17. Timing Diagram – 3-State PWM Controller, with ZCD

#### **RECOMMENDED PCB LAYOUT**

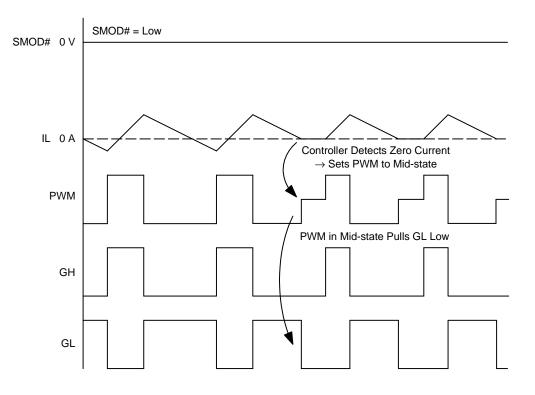

Figure 18. Top Copper Layer (Viewed from Top)

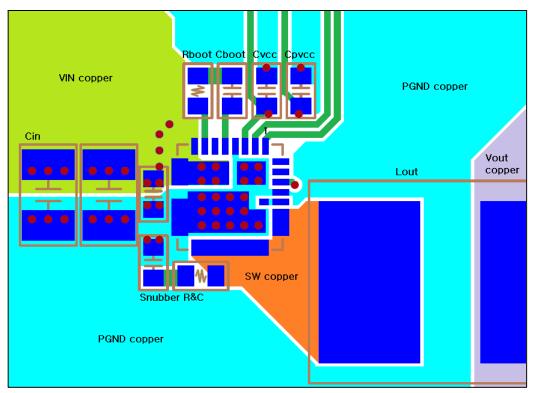

Figure 19. Bottom Copper Layer (Viewed from Top)

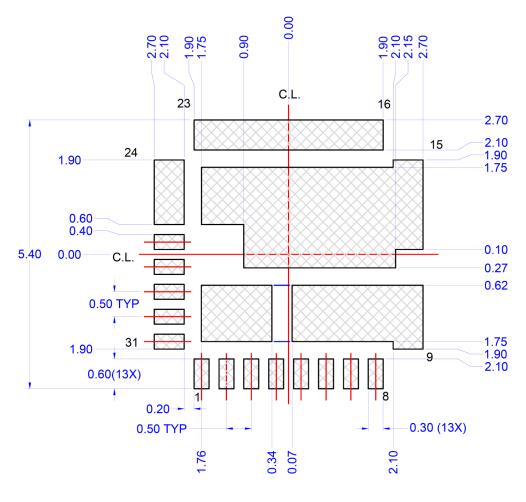

#### **RECOMMENDED PCB FOOTPRINT (OPTION 1)**

### LAND PATTERN RECOMMENDATION

#### **RECOMMENDED MOUNTING FOOTPRINT**

For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Figure 20. Recommended PCB Footprint (Option 1)

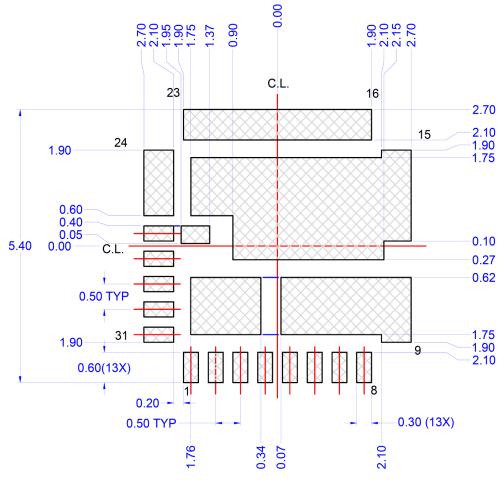

#### **RECOMMENDED PCB FOOTPRINT (OPTION 2)**

#### LAND PATTERN RECOMMENDATION

#### **RECOMMENDED MOUNTING FOOTPRINT**

For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Figure 21. Recommended PCB Footprint (Option 2)

Intel is a registered trademark of Intel Corporation in the U.S. and/or other countries.

# Onsemí.

| DOCUMENT NUMBER:                                                                                                                                                        | 98AON13680G      | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                            | PQFN31 5X5, 0.5P |                                                                                                                                                                                     | PAGE 1 OF 2 |  |  |  |

| onsemi and OOSEOD) are trademarks of Semiconductor Components Industries LLC day onsemi or its subsidiaries in the United States and/or other countries onsemi reserves |                  |                                                                                                                                                                                     |             |  |  |  |

the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights of others.

#### MECHANICAL CASE OUTLINE PACKAGE DIMENSIONS

## onsemi

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative