En guide til det grundlæggende i D flip -flops - kredsløb, sandhedstabeller, typer, fordele og begrænsninger

I digitalt kredsløbsdesign bruges flip-flops af D-type hovedsageligt i applikationer, der kræver meget stabil og præcis kontrol af dataflow.For dybt at forstå opførsel og egenskaber ved flip-flops af D-type er det et kritisk trin at konstruere og analysere en sandhedstabel.Sandhedstabeller hjælper ikke kun designere med at forudse responsen fra kredsløb, men er også et grundlæggende værktøj til at optimere kredsløbsdesign og fejldiagnose.I denne artikel vil vi udforske detaljeret den specifikke opførsel af D-typen flip-flop under forskellige input- og ursignaltilstande, forklare responsen fra dens interne logikporte gennem eksempler, og hvordan man formulerer karakteristiske tabeller og karakteristiske ligninger baseret påDisse oplysninger for at opnå mere nøjagtigt kredsløbsdesign og applikationer.Katalog

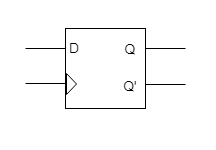

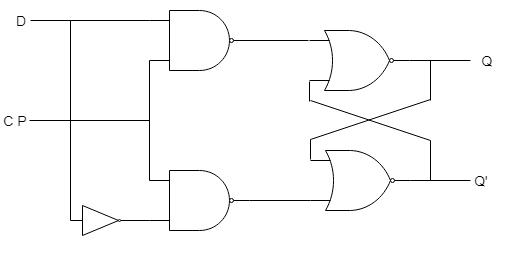

1. Arbejdsprincippet om D flip-flop

Inden vi kommer i gang, er vi nødt til at opbygge en sandhedstabel.Tabellen viser tydeligt responsen fra en D-flip-flop under forskellige input (D) og ursignalbetingelser.

Sag 1: D = 0

- • Gate 1 = 1

- • gate 2 = 0

- • Gate 4 (q (n+1) ') = 1

- • gate 3 (q (n+1)) = 0

Hvis D er lav (0), vil Q -udgangen også være lav (0).Da en af input til Gate 4 er 0, og Gate 4 er en NAND -port, vil dens output være 1 uanset de andre input på grund af NAND -portens art.

Sag 2: D = 1

- • gate 1 = 0

- • Gate 2 = 1

- • Gate 3 (q (n+1)) = 1

- • gate 4 (q (n+1) ') = 0

Hvis D er høj (1), vil Q -output gå højt (1) uanset sin tidligere tilstand.Da en af input til Gate 3 er 0, og Gate 3 er en NAND -port, vil dens output være 1 uanset de andre input på grund af NAND -portens art.

2. Situationsanalyse og sandhedstabelkonstruktion

Når man undersøger, hvordan en D-type flip-flop reagerer på forskellige inputbetingelser, er et meget kritisk trin at konstruere og forstå en sandhedstabel.Dette hjælper os med at forudsige kredsløbsadfærd og er grundlaget for fejlfinding og designoptimering.Først indstiller vi ursignalet til et kontinuerligt højt niveau (1).Dette betyder, at flip-flop reagerer på input ved D og opdaterer output ved Q i overensstemmelse hermed.

Analyser situationen, når D -indgangen er lav (0):

- Betjening: Indstil D -terminalen til 0, observer og registrer ændringerne i output.

- Logisk gate -respons: I denne opsætning er Logic Gate 1 indstillet til at udsende et højt niveau (1), mens Logic Gate 2 udsender et lavt niveau (0).

- Outputpåvirkning: Fordi NAND -porten (Gate4) modtager mindst et lavt niveau (0), i henhold til NAND -portens egenskaber, er dens output højt niveau (1).På samme tid er output fra NAND Gate 3 lav (0).

- Endelig Q -output: Dette resulterer i, at Q (n+1) 'er høj (1) og Q (n+1) er lav (0).

Analyser situationen, når D -indgangen er høj (1):

- Betjening: Indstil D -terminal til 1 på dette tidspunkt.

- Logisk gate -respons: Gate 1 udsender nu lavt (0) og Gate 2 output høje (1).

- Outputpåvirkning: Samtidig modtager NAND Gate 3 mindst et lavt niveau (0), hvilket får dens output til at blive høj (1), mens output fra NAND Gate 4 er lav (0).

- Endelig Q -output: Resultatet er, at Q (n+1) går højt (1), mens q (n+1) 'forbliver lav (0).

I henhold til ovenstående to situationer venter vi til sandhedstabellen i D-flip-flop

|

CLK |

D |

Q (n+1) |

Stat |

|

– |

0 |

0 |

NULSTIL |

|

– |

1 |

1 |

SÆT |

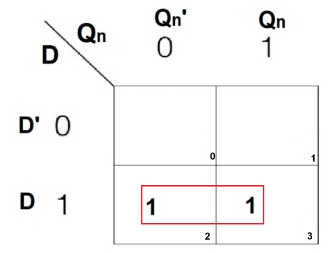

Vi kan derefter skrive egenskabstabellen for D-flip-flop baseret på denne sandhedstabel.I sandhedstabellen kan du se, at der kun er en input d og en output Q (n+1).Men i funktionstabellen vil du se, at der er to input d og q n, og en output q (n+1).

Det fremgår af ovenstående logikdiagram, at QN og QN 'er to komplementære output, der også fungerer som input til Gate3 og Gate4, så vi betragter Qn (dvs. den aktuelle tilstand af flip-flop) som input, og Q (n+1) er den næste tilstand som output.

Efter at have skrevet den karakteristiske tabel, tegner vi et 2-variabelt K-plot for at udlede den karakteristiske ligning.

|

D |

Qn |

Q (n+1) |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Fra K-MAP får du 2 par.Efter at have løst begge, får vi følgende karakteristiske ligning:

Q (n+1) = D

3. Typer af D-type flip-flops

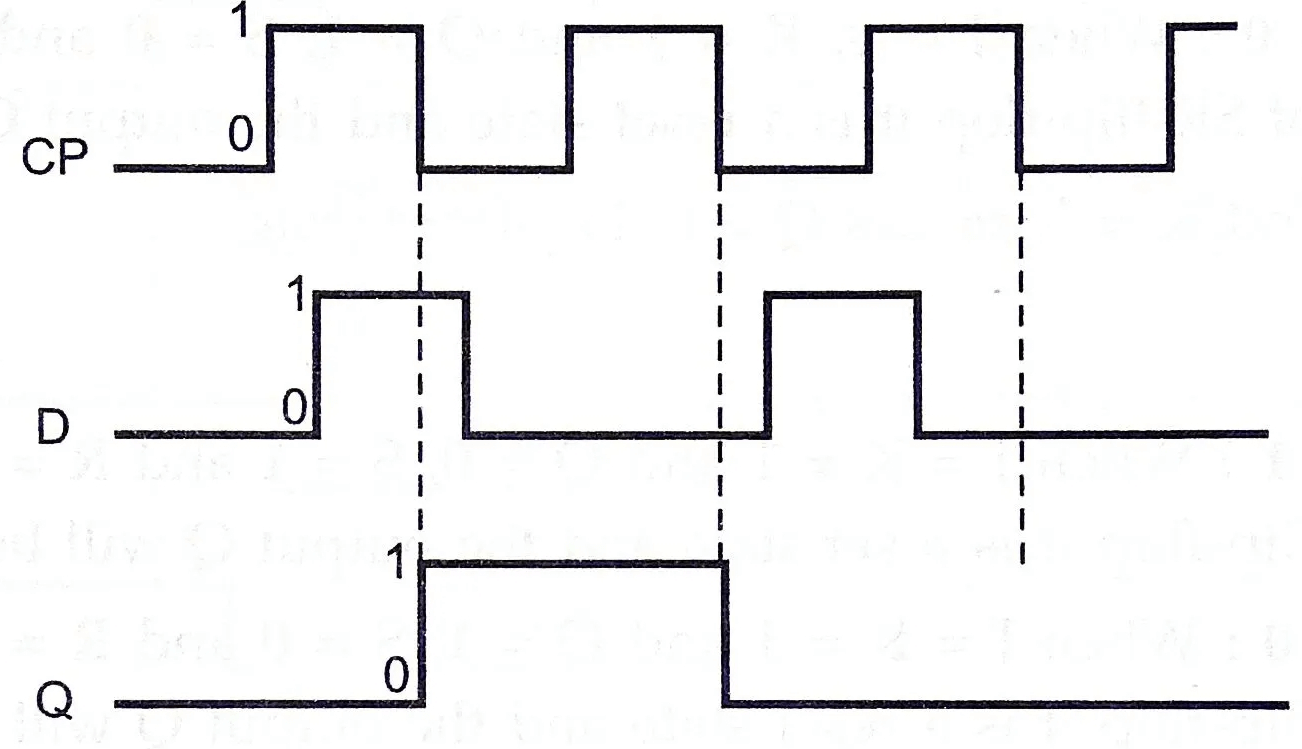

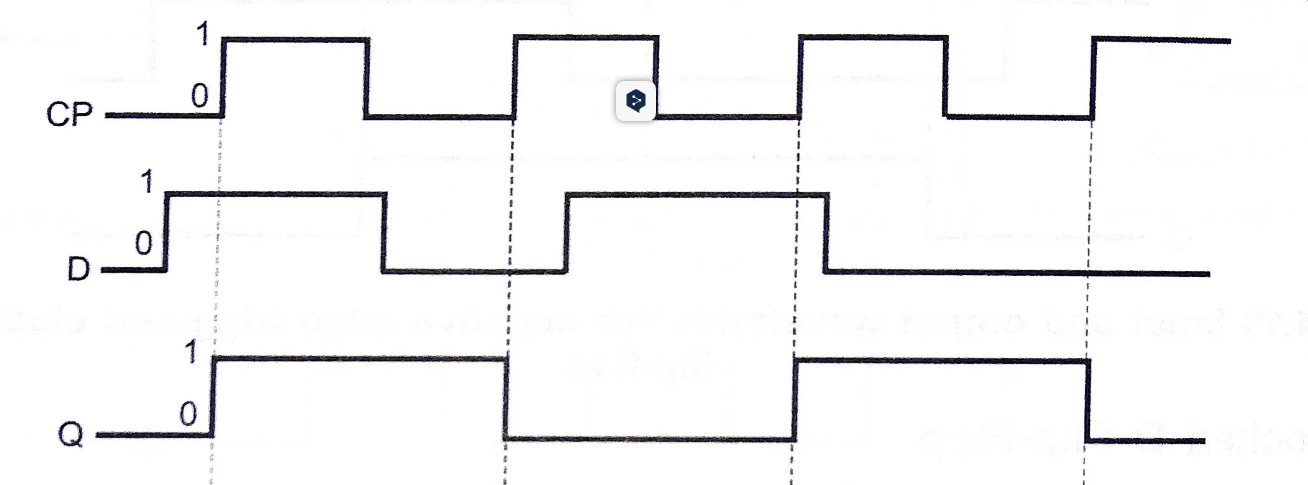

Afhængigt af hvordan uretsignalet modtages, kan D-flip-flops opdeles i to kategorier: niveau-udløste og kant-udløste.Hver type har specifikke funktioner og passende applikationer.

Level-udløst d flip-flop (Latch)

Niveau-udløste D-flip-flops, almindeligt kendt som låse, er følsomme over for de høje og lave niveauer af ursignalet.Sådan fungerer det:

- • Når ursignalet er indstillet højt (1), og input til D -terminalen ændres, afspejler output fra Q -terminalen den samme tilstand næsten øjeblikkeligt.Dette betyder, at eventuelle ændringer ved D vil blive reflekteret direkte på Q.

- • Når uretsignalet er lavt (0), forbliver output ved Q den samme uanset hvad der sker med D -terminalen.

Denne type trigger er ideel til applikationer, der kræver stabil dataoutput, såsom midlertidigt lagring af data i et dataindsamlingssystem.Latchen bevarer sin tilstand, indtil ursignalet ændres, hvilket sikrer konsistensen af dataudgangen.

Positiv kant udløset d flip-flop

En positiv kantudløst D-flip-flop reagerer kun, når urets signalet overgår fra lav til høj.Lær hvordan det fungerer:

- • Fokuser på at overvåge den stigende kant af urets signal.

- • Umiddelbart efter detektering af stigende kant overføres dataene på D -terminalen til Q -terminalen.

Denne type flip-flop er velegnet til applikationer, der kræver præcis indfangning af data på et specifikt tidspunkt, typisk i synkrone kredsløb.

Negativ kant udløset d flip-flop

Den negative kant udløste D-flip-flop er det modsatte af den positive kant, der er udløst af typen, og reagerer på det faldende kant af ursignalet.Sådan fungerer det:

- • Overvåg ursignalet for faldende kanter.

- • Når ursignalet overgår fra højt niveau til lavt niveau, fanges den aktuelle tilstand af D -terminal og overføres til Q -terminal.

Denne type flip-flop bruges i applikationer, hvor data skal indfanges på det nøjagtige øjeblik, at ursignalet falder for at sikre præcis timing i forskellige digitale systemer.

4. Fordele og begrænsninger af D-type flip-flops

Fordele

Forenklet design: D-flip-flop har en enkelt dataindgang, der forenkler det samlede kredsløbsdesign.Dette reducerer forbindelsesfejl og fremskynder implementering af layout, især under hurtig prototype af komplekse kredsløb.Når man arbejder med komplekse design, betyder færre forbindelser mindre potentiale for fejl, hvilket gør processen glattere og mere effektiv.

Stabilitet og pålidelighed: Designet af D-flip-flop eliminerer feedback-løkker, hvilket gør det mindre modtageligt for raceforhold og støj.For eksempel sikrer robustheden af D-flip-flop ensartet ydelse i miljøer med alvorlig elektrisk interferens.

Lavt effektforbrug: D flip-flops forbruger mindre strøm sammenlignet med andre flip-flops.Dette udvider batteriets levetid og reducerer driftsomkostningerne, hvilket gør det ideelt til bærbart og fjernovervågningsudstyr.I batteridrevne systemer kan brug af en D-flip-flop markant forlænge enhedens levetid markant.

Bistable operation: D flip-flops kan opretholde deres tilstand uden at ændre indgangssignalet, hvilket gør dem meget nyttige i applikationer, der kræver langvarig tilstandsopbevaring, hvilket kan være meget værdifuldt for automatiserede kontrol- og sikkerhedssystemer.

Begrænsninger

Mangel på feedbackkontrol: D Flip-FLOPS har ingen indbygget feedback-sti, hvilket gør dem uegnet til systemer, der kræver dynamisk outputjustering, såsom Servo Motor Control eller Adaptive Signal Processing.Denne begrænsning kan være vigtig i applikationer, der kræver kontinuerlig feedback for at justere output i realtid.

Forsikringsforsinkelse: Selvom d flip-flops generelt reagerer hurtigt, udviser de stadig en vis forplantningsforsinkelse.I højhastigheds digitale kommunikationssystemer kan denne forsinkelse forårsage datasynkroniseringsproblemer.Designere skal redegøre for denne forsinkelse for at undgå timingfejl i hurtige miljøer.

Skalerbarhedsproblemer: Selvom D-flip-flops er egnede til mange standardapplikationer, kan de stå over for udfordringer, når de skaleres til mere komplekse digitale systemer.Håndtering af mere samtidige signaler eller højere datahastigheder kan komplicere systemdesign, øge vanskeligheder og omkostninger.Når systemkompleksiteten øges, bliver begrænsningerne af D-flip-flops til styring af store mængder signalbehandling mere tydelige.

5. Anvendelsesområder

D flip-flops har en række praktiske applikationer i digitale systemer.Nogle vigtige anvendelser inkluderer:

Skiftregistre: Ved at kaskader flere D-flip-flops kan du oprette skiftregistre, der gemmer og skifter data i digitale systemer.Skiftregistre bruges ofte i seriel kommunikationsprotokoller som UART, SPI og I2C.I praksis kan du bruge dem til at konvertere data mellem serielle og parallelle former og således lette effektiv dataoverførsel.

Statsmaskine: D Flip-FLOPS er en integreret del af implementeringen af en tilstandsmaskine, der styrer rækkefølgen af begivenheder i et digitalt system.Statlige maskiner er allestedsnærværende i kontrolsystemer, bilapplikationer og industriel automatisering.I en automatiseret produktionslinie kan en statsmaskine for eksempel styre rækkefølgen af operationer, hvilket sikrer, at hvert trin udføres i orden.

Tællere: Kombination af D-flip-flops med andre digitale logiske porte kan skabe binære tællere, der tæller op eller ned afhængigt af designkravene.Disse tællere er afgørende i realtidsapplikationer såsom timere og ure.I et digitalt ur hjælper en tæller for eksempel at spore tidens gang ved at tælle urimpulser.

Datalagring: D flip-flops kan gemme midlertidige data i digitale systemer.De bruges ofte sammen med andre lagringselementer til at bygge mere komplekse lagringssystemer.F.eks. I en computers hukommelsesarkitektur kan en D-flip-flop midlertidigt gemme bits af data som en del af en større hukommelsesstruktur.

6. Resumé

Uanset om det er i forskellige praktiske applikationer, såsom datalagring, tilstandskontrol eller præcis timing, har D-type flip-flops vist deres kraftfulde funktionalitet.Deres design forenkler kredsløbskompleksiteten, forbedrer systemstabiliteten og pålideligheden og reducerer strømforbruget.Som designer vil det at forstå de detaljerede arbejdsmekanismer og potentielle anvendelser af disse flip-flops hjælpe dig med bedre at bruge disse enheder til at løse specifikke tekniske udfordringer og derved designe mere effektive og pålidelige digitale systemer.

Jeg håber, at denne artikel er nyttig for dig.Hvis du har brug for at udforske mere teknisk viden om flip-flops af D-type, kan du kontakte os.

Ofte stillede spørgsmål [FAQ]

1. Hvordan fungerer en D-flip-flop?

D flip-flop (d flip-flop) er en elektronisk komponent, der hovedsageligt bruges til at gemme signaltilstande.På den stigende kant af ursignalet lyder D Flip-Flop og låser signaltilstanden ved D-indgangen indtil den næste stigende kant af ursignalet.Specifikt, hvis D -terminalindgangen er højt niveau (1), vil output Q også blive højt niveau efter urpulsen;Hvis D -terminalen er lavt niveau (0), vil output Q blive lavt niveau..

2. Hvad står D i D flip-flop for?

"D" i D-flip-flop står for "data", hvilket betyder, at denne flip-flop hovedsageligt bruges til lagring og transmission af data.

3. Hvad er outputfrekvensen for D-flip-flop?

Outputfrekvensen for en D-flip-flop er lig med halvdelen af inputursignalet.Dette skyldes, at D-flip-flop kun reagerer på den ene kant af signalet (normalt den stigende kant) i hver urcyklus, så dataene opdateres kun en gang hver anden urcyklusser.

4. Hvad er forskellen mellem en D-flip-flop og en T-flip-flop?

Den største forskel mellem D-flip-flop og T-flip-flop er deres funktion og formål.D flip-flops bruges til at låse en enkelt databit og er ideelle til datalagring og signalsynkronisering.T flip-flop (skift flip-flop) skifter udgangstilstand ved hver urpuls.Hvis input er højt niveau, skifter output fra højt niveau til lavt niveau eller fra lavt niveau til højt niveau.fladt, hvilket gør T-flip-flops, der ofte bruges i tællerdesign.

5. Hvorfor bruger vi en D-flip-flop i stedet for SR-flip-flop?

Vi foretrækker at bruge D-flip-flops i stedet for SR-flip-flops (sæt-reset flip-flop), hovedsageligt fordi D flip-flops er enklere og sikrere i design.SR-flip-flop skal kontrollere sættet og nulstille signaler på samme tid.Hvis begge input er høje på samme tid, vil det få output til at indtaste en ustabil tilstand, hvilket kan forårsage problemer i praktiske anvendelser.I modsætning hertil kræver D-flip-flop kun en dataindgang, er lettere at kontrollere og ser ikke ud til at være ustabil.Derfor er D Flip-FLOP mere foretrukket i applikationer, der kræver stabil datalagring og forenklet design.