T Trigger Knowledge Guide - Pros og Ulemper, hvordan det fungerer, typer

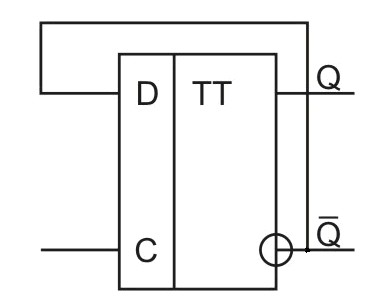

T-flip-flops ligner JK-flip-flops.Ved at tilslutte J- og K-indgange kan man udlede en T-flip-flop.Som en D-flip-flop har den kun et eksternt input sammen med et ur.

Katalog

Hvordan T-flip-flops fungerer

Flip-flops er de enkleste enheder i digitale automater, der udviser to stabile tilstande.Den ene stat har en værdi på "1" og den anden en "0."Enhedens tilstand og de binære oplysninger, der er gemt i den, bestemmes af outputsignalerne: direkte og omvendt.Hvis der er indstillet et potentiale på den direkte output, der svarer til den logiske output, er enheden i en enkelt-triggertilstand (den inverse outputs potentiale svarer til logisk nul).Hvis der ikke er noget potentiale på den direkte output, er enheden i nulstaten.

Typer af T-flip-flops

T-flip-flops kommer primært i to sorter:

Asynkron t-trigger

Synkron T-trigger

Begge typer T-flip-flops fungerer på lignende måde.Den eneste forskel er i færd med at skifte fra en stat til en anden.Den asynkrone type udfører denne overgang direkte, mens den synkrone type fungerer baseret på dette signal.

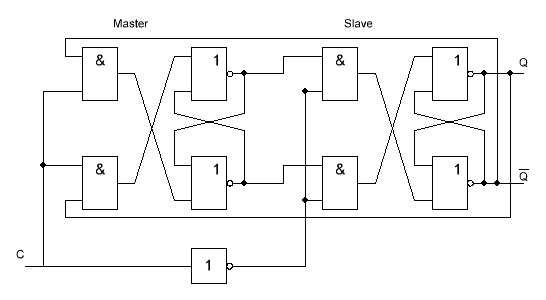

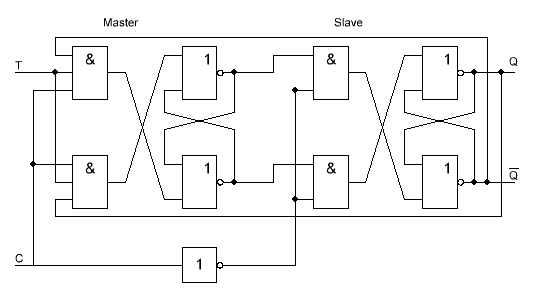

Ved evaluering af et scenarie, hvor urindgangen altid er høj (1), er det nødvendigt at overveje de to potentielle tilstande for skiften (T), enten høj (1) eller lav (0).Lad os detaljerede resultaterne for hver stat og de involverede logiske gate -interaktioner.

Sag 1: t = 0

- Outputtilstand: Her er både Gate1 og Gate2 og porte tilsluttet T (indstillet til 0).

- Gate1 og Gate2 Output: Da en og gate output 0, når nogen af dens input er 0, vil output fra Gate1 og Gate2 altid være 0, uanset deres andre input.

- Gate3/Q (n+1) Logik: Gate3 påvirkes af output fra Gate1.Når Gate1 udsender 0, forenkler Gate3's logiske ligning til ikke (0 eller ikke Q), hvilket resulterer i Q.

- Gate4/Q (n+1) 'Logik: Gate4 følger et lignende mønster, der ikke producerer (0 eller q), der forenkler til ikke q eller q'.

Sag 1 SAMMENDRAG:

- Forudsat at gate1 = 0 og gate2 = 0 og ved hjælp af karakteristikken for og porte (ethvert input på 0 resulterer i et output på 0), er operationen ligetil:

- Gate3/q (n+1) beregner som q og opretholder den aktuelle tilstand.

- Gate4/q (n+1) 'resulterer i q', komplementet til den aktuelle tilstand.

Sag 2: t = 1

- Outputtilstand: Når T er indstillet til 1, afspejler indgange fra Gate1 og Gate2 nu output fra andre logiske operationer, hvilket påvirker deres output.

- Gate1 og Gate2 Output: Gate1 forbinder direkte til den aktuelle tilstand Q og Gate2 til ikke Q eller Q '.

- Gate4/Q (n+1) 'Logik: Her forenkler ligningen, fordi input fra og gate er modsætninger (q og ikke q), hvilket resulterer i 0.

- GATE3/Q (N+1) Logik: På den anden side omhandler Gate3 ikke Q eller Q ', der ikke udsendes (Q og 0), der forenkler til ikke Q eller Q'.

Sag 2 SAMMENDRAG:

- Logikopsætningen fører til interessante interaktioner:

- Gate1 = q, gate2 = q ', der påvirker efterfølgende logiske processer.

- Gate4/q (n+1) 'beregner direkte som 0, da driften mellem Q og ikke Q ikke kan være sand.

- Gate3/q (n+1) beregner derefter som q ', som er skiften fra den forrige tilstand, da t var 0.

T Flip-flop sandhedstabel

|

CLK |

T |

Q (n+1) |

Tilstand |

|

|

0 |

Q |

Ingen ændring |

|

|

1 |

Q ' |

Skift |

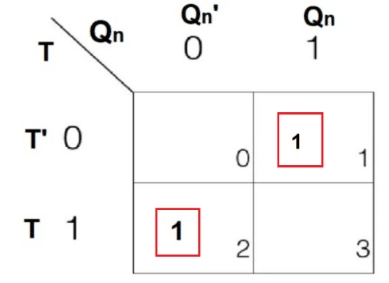

Vi bruger denne sandhedstabel til at kompilere en karakteristisk tabel til T-flip-flop.I sandhedstabellen kan du kun se en input T og en output Q (n+1).I den karakteristiske tabel vil du dog se to input T og QN og en output Q (n+1).

Fra logikdiagrammet ovenfor er det tydeligt, at Qn og Qn 'er to komplementære output, der også fungerer som input til Gate3 og Gate4, derfor betragter vi Qn (dvs. den aktuelle tilstand af flip-flop) som input, og Q (n+1) som output til den næste tilstand.

Efter afsluttet den karakteristiske tabel konstruerer vi et 2-variabelt K-MAP for at udlede den karakteristiske ligning.

|

T |

Qn |

Q (n+1) |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0

|

Fra K-MAP får du to par.Løsning af begge får vi følgende karakteristiske ligning:

Q (n + 1) = tqn ' + t’qn = t xor qn

Fordele ved at bruge T-flip-flops

I digitale kredsløb tilbyder T-flip-flops flere betydelige fordele, der forenkler deres funktion og integration:

- Enkelt input enkelhed: T-flip-flops har kun et input, der forenkler deres drift.Dette enkelt input kan skifte mellem høje og lave tilstande, så det problemfrit integreres i kredsløbsdesign og forbinder let med andre digitale kredsløb.

- Ingen ugyldige siger: T-flip-flops mangler ugyldige tilstande, hvilket hjælper med at forhindre uforudsigelig opførsel i digitale systemer.Denne pålidelighed er afgørende for at opretholde en ensartet systemydelse.

- Nedsat strømforbrug: Sammenlignet med andre flip-flops forbruger T-flip-flops mindre strøm.Denne energieffektivitet er gavnlig til at udvide batteriets levetid på bærbare enheder og reducere energiomkostningerne ved store digitale systemer.

- Bistable operation: Som andre flip-flops har T-flip-flops bistabel drift, hvilket betyder, at de på ubestemt tid kan holde enten tilstand (0 eller 1), indtil de udløses af et indgangssignal.Denne egenskab er vigtig for applikationer, der kræver stabil, langvarig opbevaring af enkeltbitdata.

- Let implementering: T-flip-flops kan let implementeres ved hjælp af grundlæggende logiske porte.Denne enkelhed gør dem til et økonomisk levedygtigt valg for mange digitale systemer, hvilket hjælper med at reducere de samlede systemomkostninger.

Begrænsninger af T-flip-flops

På trods af disse fordele har T-flip-flops også nogle begrænsninger, der kan påvirke deres egnethed til visse applikationer:

- Inverteret output: Outputet fra T-FLIP-FLOPS er det modsatte af dets input, som kan komplicere designet af timinglogikkredsløb og gøre designet mere komplekst.Designere skal overveje dette for at sikre korrekt kredsløbsadfærd.

- Begrænset funktionalitet: T-flip-flops kan kun gemme en smule information og er ikke i stand til at udføre komplekse operationer som tilføjelse eller multiplikation, hvilket begrænser deres anvendelse i grundlæggende hukommelsesopgaver.

- Følsomhed over for fejl: T-flip-flops kan være følsomme over for fejl og støj på indgangssignalet, hvilket potentielt forårsager uventede tilstandsændringer.Denne følsomhed kan føre til uforudsigelig opførsel i digitale systemer, især i miljøer med høj elektronisk interferens.

- Forsikringsforsinkelse: Som alle flip-flops støder t-flip-flops forplantningsforsinkelser, som kan indføre timingproblemer i systemer med strenge timingbegrænsninger.Disse forsinkelser skal overvejes under systemdesign for at undgå timingfejl og sikre pålidelig drift.

Applikationer

T-flip-flops bruges i forskellige applikationer i den virkelige verden, herunder:

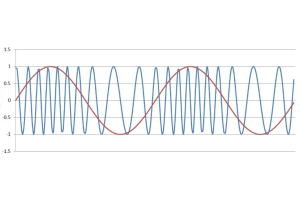

- Frekvensafdeling: T-flip-flops bruges ofte til at halvere hyppigheden af et ursignal.Ved at skifte tilstand af flip-flop med hver urpuls deler de effektivt frekvensen af indgangssignalet med to, hvilket gør dem ideelle til præcis timing og digitale ure og frekvenssynthesizere.

- Frekvens fordobling: Omvendt kan T-flip-flops også bruges til at fordoble hyppigheden af et ursignal, kendt som frekvensdobling.Dette opnås ved at konfigurere flip-flops i en opsætning, der genererer en outputfrekvens dobbelt så stor som indgangssignalet.

- Datalagring: T-flip-flops kan bruges som basale byggesten til lagring af enkeltdatabits, hvor data skal midlertidigt gemmes for yderligere behandling eller transmission.Dette gør dem meget nyttige i applikationer såsom skiftregistre og lagerenheder.

- Tællere: En anden signifikant anvendelse af T-flip-flops er at skabe binære tællere.De kan sammenkobles med andre digitale logiske porte til konstruktion af tællere, der kan øge eller nedlægge tælling baseret på designkrav.

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

→ Tidligere

At forstå din bils batterikapacitet og hvordan den fungerer under forskellige forhold er vigtig for enhver bilejer, især når man står over for ekstreme vejrudfordringer.Den kolde cranking AMPS (CCA) -rating er en uundværlig foranstaltning til at måle et batteris kapacitet til at starte en moto...

At udforske dynamikken på 1,5V batterier afslører ikke kun deres kritiske rolle i at drive en forskelligartet række enheder, men også deres rige historiske og teknologiske kontekst.Disse batterier, der findes i forskellige former, såsom AA, AAA, C og D -celler, er blevet uundværlige i både hv...

→ Næste

Hvor meget ved du om CCA?

på 2024-04-26

1,5V batteri —— Hvor meget ved du?

på 2024-04-25

Populære indlæg

-

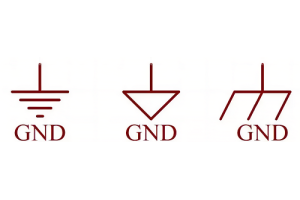

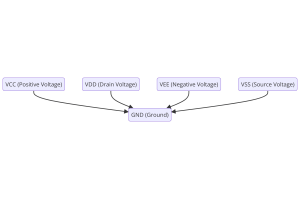

Hvad er GND i kredsløbet?

på 1970-01-01 3272

-

RJ-45 Connector Guide: RJ-45 Stikfarvekoder, ledningsordninger, R-J45-applikationer, RJ-45 datablad

på 1970-01-01 2815

-

Forståelse af strømforsyningsspændinger i elektronik VCC, VDD, VEE, VSS og GND

på 0400-11-20 2642

-

Fiberstikstyper: SC vs LC og LC vs MTP

på 1970-01-01 2265

-

Sammenligning mellem DB9 og RS232

på 1970-01-01 1882

-

Hvad er et LR44 -batteri?

Elektricitet, den allestedsnærværende kraft, roligt gennemsyrer alle aspekter af vores daglige liv, fra trivielle gadgets til livstruende medicinsk udstyr, det spiller en stille rolle.Imidlertid er det ingen let opgave at gribe ind i denne energi, især hvordan man opbevarer og effektivt udsender den.Det er på denne baggrund, at denne artikel vil fokusere på en type møntcellebatteri, der kan ...på 1970-01-01 1846

-

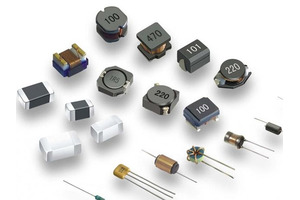

Forståelse af de grundlæggende elementer: induktansresistens, og kapacitet

I den komplicerede dans inden for elektroteknik tager en trio af grundlæggende elementer centrum: induktans, modstand og kapacitans.Hver bærer unikke træk, der dikterer de dynamiske rytmer af elektroniske kredsløb.Her går vi på en rejse for at dechiffrere kompleksiteten af disse komponenter for at afsløre deres forskellige roller og praktiske anvendelser inden for det store elektriske o...på 1970-01-01 1808

-

Hvad er RF, og hvorfor bruger vi det?

Radiofrekvens (RF) -teknologi er en vigtig del af moderne trådløs kommunikation, der muliggør datatransmission over lange afstande uden fysiske forbindelser.Denne artikel dækker det grundlæggende i RF og forklarer, hvordan elektromagnetisk stråling (EMR) gør RF -kommunikation mulig.Vi vil udforske principperne for EMR, oprettelse og kontrol af RF-signaler og deres omfattende anvendelser.Art...på 1970-01-01 1801

-

CR2430 Batteri Comprehensive Guide: Specifikationer, applikationer og sammenligning med CR2032 -batterier

Hvad er CR2430 -batteri?Fordele ved CR2430 -batterierNormCR2430 Batteri applikationerCR2430 ækvivalentCR2430 vs CR2032Batteri CR2430 størrelseHvad man skal kigge efter, når man køber CR2430 og ækvivalenterDatablad PDFOfte stillede spørgsmål Batterier er hjertet i små elektroniske enheder.Blandt de mange tilgængelige typer spiller møntceller en afgørende rolle, der ofte findes i regnemas...på 1970-01-01 1799

-

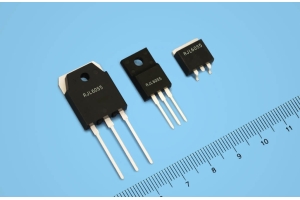

Omfattende guide til HFE i transistorer

Transistorer er afgørende komponenter i moderne elektroniske enheder, hvilket muliggør signalforstærkning og kontrol.Denne artikel dækker i viden omkring HFE, herunder hvordan man vælger en transistors HFE -værdi, hvordan man finder HFE og gevinsten af forskellige typer transistorer.Gennem vores udforskning af HFE får vi en dybere forståelse af, hvordan transistorer fungerer og deres rolle...på 5600-11-20 1782