HjemBlogSR Flip-Flop Knowledge Guide-Arbejdsprincip, fordele, ulemper, sandhedstabel og forskelle fra Rs flip-flop

SR Flip-Flop Knowledge Guide-Arbejdsprincip, fordele, ulemper, sandhedstabel og forskelle fra Rs flip-flop

En flip-flop er simpelthen et udtryk, der henviser til en digital elektronisk enhed, som er en elektronisk komponent, der bruges til at gemme en enkelt bit information.

SR-flip-flop (sæt-reset flip-flop) er en grundlæggende komponent i digitale elektroniske kredsløb, der bruges til lagring og manipulering af data.Det fungerer på en sekventiel måde.SR-flip-flops kan konstrueres ved hjælp af SR-låse.En lås er et digitalt elektronisk kredsløb, der tager den enkle form for et lagerelement, der er i stand til at gemme en bit binær information (0 eller 1).I denne artikel vil vi diskutere SR-flip-flop, inklusive dets arbejdsprincip, sandhedstabel, fordele, ulemper og forskelle fra RS-flip-flop.

Katalog

1. SR-flip-flop arbejdsprincip

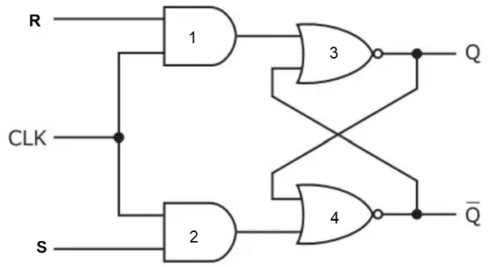

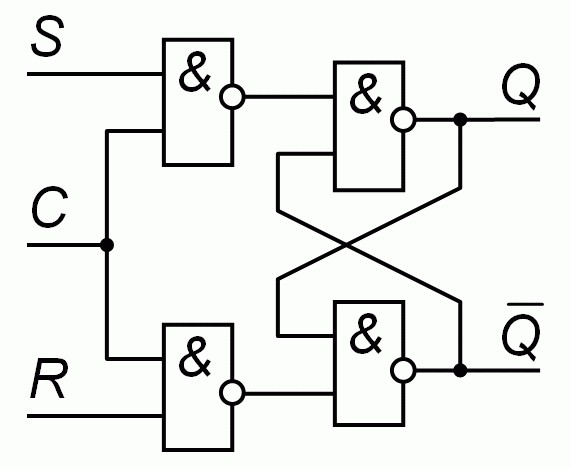

Den enkleste RS-flip-flop kan bygges ved hjælp af to 2-input eller porte, som vist på diagrammet:

Bemærk, at den måde, elementerne er tilsluttet, sikrer, at de altid er i modsatte tilstande.Hvis output fra det første element er 1, vil output fra det andet element være 0, og vice versa.

For at lette forståelsen er her de fire scenarier, der kan forekomme med en SR-flip-flop:

Scenario 1: S = 0, r = 0

GATE OUTPUT: Både Gate1 og Gate2 Output 0. Statlige vedligeholdelse: Da porte 3 og 4 er heller ikke porte, med et input til 0, afhænger deres output af det andet input.Gate3/Q (n+1) bevarer således den forrige tilstand q, og gate4/q (n+1) 'bevarer den komplementære tilstand q'.

Scenario 2: S = 0, r = 1

Gate Output: Gate1 Output 1 (da R er høj), Gate2 -udgange 0. Nulstil drift: For Gate3 er et input højt (fra gate1), hvilket fører til en output på 0 via NOR -operationen, hvilket nulstiller staten.En input til Gate4 forbliver imidlertid lavt, udsendt 1, hvilket indikerer den komplementære tilstand.

Scenarie 3: S = 1, r = 0

Gate output: gate1 output 0, gate2 output 1 (da s er høj).Indstil drift: På dette tidspunkt udsender Gate3 1 (den anden input fra Gate1 er lav), der indstiller flip-flop.Omvendt, på grund af det høje input fra Gate2, udsender Gate4 output 0, der bekræfter den komplementære tilstand.

Scenario 4: S = 1, r = 1

Gate Output: Med begge input høje, output fra begge porte 1. Ugyldig tilstand: Når begge input er høje, skal porte 3 og 4 både output 0, hvilket resulterer i en konflikt, fordi q (n+1) og q (n+1) 'skalVær komplementære output, men dette er ikke tilfældet, hvilket fører til, at denne tilstand er ugyldig.

2. Sr flip-flop sandhedstabel

|

S |

R |

Q (n+1) |

Stat |

|

0 |

0 |

Qn |

Ingen ændring |

|

0 |

1 |

0 |

NULSTIL |

|

1 |

0 |

1 |

SÆT |

|

1 |

1 |

x |

Ugyldig |

Vi bruger denne sandhedstabel til at skrive den karakteristiske tabel til SR-flip-flop.I sandhedstabellen kan du se to input, S og R og en output, Q (n+1).I den karakteristiske tabel vil du imidlertid se tre input, S, R og QN og en output, Q (N+1).

Fra logikdiagrammet er det klart, at QN og QN 'er to komplementære output, der også fungerer som input til porte 3 og 4, så vi betragter Qn, den aktuelle tilstand af flip-flop, som input, og Q (n+1), den næste tilstand, som en output.

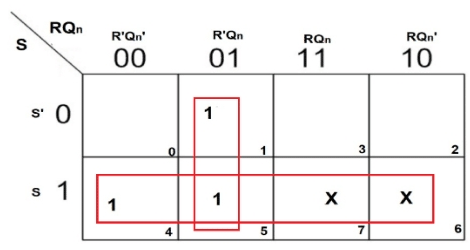

Efter at have skrevet den karakteristiske tabel, tegner vi et 3-variabelt K-MAP for at udlede den karakteristiske ligning.

3. Karakteristisk tabel

|

S |

R |

Qn |

Q (n+1) |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

x |

|

1 |

1 |

1 |

x |

Fra K-MAP får du to par.Efter løsning af begge dele opnår vi følgende karakteristiske ligning:

Q (n + 1) = s + r'qn

4. Fordele ved SR-flip-flop

Brug af SR-flip-flops har flere fordele.Nedenfor er nogle af dem:

- Enkelhed: Designet af SR-flip-flops er relativt enkel, kun bestående af nogle få porte.De kan let integreres i større kredsløb uden at komplicere det overordnede design.

- Hastighed: SR-flip-flops fungerer i høj hastighed.De kan hurtigt skifte mellem sæt og nulstille tilstande uden forsinkelse, hvilket sikrer, at digitale systemer kan udføre opgaver mere effektivt og derved forbedre ydelsen af teknologier, der er afhængige af hurtig databehandling.

- Lavt strømforbrug: SR-flip-flops forbruger meget lidt strøm, hvilket gør dem ideelle til brug i batteridrevne enheder, såsom mobiltelefoner og bærbare computerenheder, samtidig med at de betyder lavere driftsomkostninger med hensyn til energiforbrug.

- Bistabel drift: SR-flip-flops kan på ubestemt tid opretholde en tilstand (indstillet eller nulstilling), indtil et indgangssignal beder om en ændring, og evnen til at opretholde en stabil tilstand uden konstant input gør SR-flip-flops nyttige til forskellige applikationer.

5. Begrænsninger af SR-flip-flops

På trods af flere fordele har SR-flip-flops også nogle begrænsninger.Nedenfor er nogle af dem:

- Raceforhold: SR-flip-flops er modtagelige for raceforhold, hvor outputtilstanden kan ændre sig uforudsigeligt på grund af ændringer i tidspunktet for indgangssignaler, hvilket potentielt fører til fejl eller uventede resultater.

- Ugyldig tilstand: En iboende begrænsning af SR-flip-flops er deres opførsel, når både sæt (er) og nulstilling (R) -indgange er aktive samtidig.I dette tilfælde går flip-flop ind i en ugyldig tilstand, hvilket ofte resulterer i, at begge output er høje eller lave, hvilket krænker det grundlæggende driftsprincip for en bistabel enhed.Denne ugyldige tilstand kan forstyrre den normale funktion af digitale kredsløb, hvilket fører til uforudsigelig systemadfærd og potentielt datatab.

- Begrænset skalerbarhed: SR-flip-flops kan være vanskelige at skalere til mere komplekse digitale systemer, når systemets kompleksitet øges, sandsynligheden for at indføre fejl på grund af den grundlæggende karakter af SR-flip-flops øges også.

6. Anvendelsesområder

- Kontrolsystemer: I kontrolsystemer kan SR-flip-flops opnå glatte overgange mellem signaler og derved minimere ulykkesrisici og forbedre trafikstrømmen.En almindelig applikation er i trafiklysstyringssystemer, hvor SR-flip-flops hjælper med at styre sekvensen af trafiklys, hvilket sikrer signalerændring på en præcis og ordnet måde og derved sikkert og effektivt kontrollerende trafikstrøm.

- Hukommelseslagring: SR-flip-flops er også grundlæggende komponenter i hukommelseslagringsenheder såsom registre.De bruges til midlertidigt at gemme data i computerenheder, der spænder fra mikroprocessorer til digitale signalprocessorer, hvilket giver mulighed for hurtig adgang og manipulation af data under behandlingsopgaver.

- Digitale tællere: SR-flip-flops bruges i digitale tællere til tælling af operationer, hvilket muliggør stigning eller dekrementering baseret på indgangssignaler.

- Datasynkronisering: SR-flip-flops er afgørende for at synkronisere datasignaler mellem to digitale kredsløb, hvilket sikrer, at de fungerer samtidig inden for den samme urcyklus, hvilket er meget nyttigt til at opretholde pålideligheden af kommunikationsnetværk.

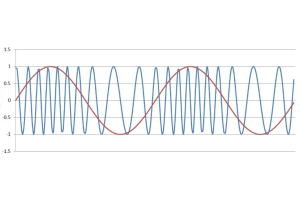

- Oscillatorer: Når de kombineres med andre komponenter, kan SR-flip-flops danne enkle oscillatorer, der producerer periodiske signaler.Dette er især nyttigt i applikationer som urkredsløb og lydsignalgeneratorer, hvor der er behov for konsistent og stabil signalgenerering.

7. Forskelle mellem SR og RS flip-flops

|

Funktion |

SR-flip-flop |

Rs flip-flop |

|

S = 0 , r = 0 |

Q tilstand (ingen ændring) opretholdt. |

Q tilstand (ingen ændring) opretholdt. |

|

S = 0 , r = 1 |

Nulstil (q = 0) |

Nulstil (q = 0) |

|

S = 1 , r = 0 |

Sæt (q = 1) |

Sæt (q = 1) |

|

S = 1 , r = 1 |

Sæt (dominerende) (q = 1) |

Nulstil (dominerende) (q = 0) |

|

Fordele: |

Når S og R begge er 1, er den indstillede operation

har forrang. |

Når S og R begge er 1, er nulstillingsoperationen

har forrang. |

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

→ Tidligere

Ofte overset, men meget markant, AG1 -batterier giver en række enheder fra hverdagens gadgets til medicinsk udstyr.AG1 -batterier, der fås i både alkaliske og sølvoxidvarianter, imødekommer forskellige behov ved at tilvejebringe forskellige spændingsudgange og stabilitetsniveauer.Den alkaliske...

At forstå din bils batterikapacitet og hvordan den fungerer under forskellige forhold er vigtig for enhver bilejer, især når man står over for ekstreme vejrudfordringer.Den kolde cranking AMPS (CCA) -rating er en uundværlig foranstaltning til at måle et batteris kapacitet til at starte en moto...

→ Næste

AG1 batteriækvivalente udskiftninger

på 2024-04-27

Hvor meget ved du om CCA?

på 2024-04-26

Populære indlæg

-

Hvad er GND i kredsløbet?

på 1970-01-01 2946

-

RJ-45 Connector Guide: RJ-45 Stikfarvekoder, ledningsordninger, R-J45-applikationer, RJ-45 datablad

på 1970-01-01 2502

-

Fiberstikstyper: SC vs LC og LC vs MTP

på 1970-01-01 2091

-

Forståelse af strømforsyningsspændinger i elektronik VCC, VDD, VEE, VSS og GND

på 0400-11-09 1898

-

Sammenligning mellem DB9 og RS232

på 1970-01-01 1765

-

Hvad er et LR44 -batteri?

Elektricitet, den allestedsnærværende kraft, roligt gennemsyrer alle aspekter af vores daglige liv, fra trivielle gadgets til livstruende medicinsk udstyr, det spiller en stille rolle.Imidlertid er det ingen let opgave at gribe ind i denne energi, især hvordan man opbevarer og effektivt udsender den.Det er på denne baggrund, at denne artikel vil fokusere på en type møntcellebatteri, der kan ...på 1970-01-01 1714

-

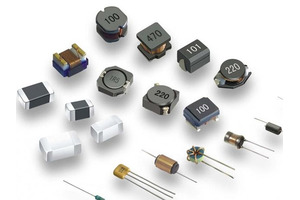

Forståelse af de grundlæggende elementer: induktansresistens, og kapacitet

I den komplicerede dans inden for elektroteknik tager en trio af grundlæggende elementer centrum: induktans, modstand og kapacitans.Hver bærer unikke træk, der dikterer de dynamiske rytmer af elektroniske kredsløb.Her går vi på en rejse for at dechiffrere kompleksiteten af disse komponenter for at afsløre deres forskellige roller og praktiske anvendelser inden for det store elektriske o...på 1970-01-01 1662

-

CR2430 Batteri Comprehensive Guide: Specifikationer, applikationer og sammenligning med CR2032 -batterier

Hvad er CR2430 -batteri?Fordele ved CR2430 -batterierNormCR2430 Batteri applikationerCR2430 ækvivalentCR2430 vs CR2032Batteri CR2430 størrelseHvad man skal kigge efter, når man køber CR2430 og ækvivalenterDatablad PDFOfte stillede spørgsmål Batterier er hjertet i små elektroniske enheder.Blandt de mange tilgængelige typer spiller møntceller en afgørende rolle, der ofte findes i regnemas...på 1970-01-01 1567

-

Hvad er RF, og hvorfor bruger vi det?

Radiofrekvens (RF) -teknologi er en vigtig del af moderne trådløs kommunikation, der muliggør datatransmission over lange afstande uden fysiske forbindelser.Denne artikel dækker det grundlæggende i RF og forklarer, hvordan elektromagnetisk stråling (EMR) gør RF -kommunikation mulig.Vi vil udforske principperne for EMR, oprettelse og kontrol af RF-signaler og deres omfattende anvendelser.Art...på 1970-01-01 1550

-

CR2450 vs CR2032: Kan batteriet bruges i stedet?

Lithium -manganbatterier har nogle ligheder med andre lithiumbatterier.Høj energitæthed og lang levetid er de egenskaber, de har til fælles.Denne form for batteri har vundet tillid og fordel for mange forbrugere på grund af dens unikke sikkerhed.Dyre tech -gadgets?Små apparater i vores hjem?Se dig omkring, så ser du dem overalt.Blandt disse mange lithium-manganske batterier er CR2450-batteri...på 1970-01-01 1519