CPLD forklarede: En guide til programmerbare logiske enheder

I den dynamiske verden af elektronisk design skiller komplekse programmerbare logiske enheder (CPLD'er) sig ud som alsidige værktøjer, og blandes problemfrit tilpasningsevne, præcision og effektivitet.Disse enheder revolutionerede kredsløbsdesign ved at introducere programmerbare makroceller og en dominerende sammenkoblingsmatrix, hvilket muliggør oprettelse af indviklede logiske funktioner med en bemærkelsesværdig pålidelighed.Fra deres start i 1980'erne til deres nøglerolle i moderne industrier som netværk, bilindustrien og rumfart, har CPLDS vist sig at være nødvendig for, at du søger både fleksibilitet og ydeevne.Denne artikel graver sig ned i CPLD'ernes rejse, deres karakteristiske funktioner, praktiske applikationer og programmeringsmetodologierne, der gør dem til en hjørnesten i digital logisk design.Katalog

Oversigt over CPLD

Inden for dominionen af komplekse programmerbare logiske enheder (CPLDS) opdager man en sofistikeret tapestry af programmerbare logiske makroceller, vævet gennem en dominerende interconnect -matrix.Disse makrocelle (MC) og input/output (I/O) enhedslinjer giver dig mulighed for dybt at designe kredsløb og konfigurere strukturer til unikke funktioner.I modsætning til enheder, der er forvirrede af deres indviklede sammenkoblingstiming, bruger CPLDS fastmeste metaltråde.Denne karakteristik giver dem en konsekvent og forudsigelig uradfærd, hvilket gør timing -forudsigelser mere pålidelige og præcise.

Rejsen og udnyttelsen

1970'erne indledte fremkomsten af programmerbare logiske enheder (PLDS), der fremmer en bevægelse mod programmerbare makroenheder.Dette skift introducerede rigelig designfleksibilitet og adskiller dem fra statiske digitale kredsløb, skønt deres anvendelighed oprindeligt blev begrænset til enklere kredsløb.Fremkomsten af CPLD'er i midten af 1980'erne revolutionerede dette landskab og banede vejen for komplekse kredsløbsdesign.Siden da har de vævet sig ind i stoffet fra industrier som netværk, bilelektronik, CNC -bearbejdning og rumfartssystemer.Du kan minde om, hvordan CPLDS forenklede processer, der engang krævede omhyggelig manuel arbejdskraft, der markerer et bemærkelsesværdigt spring i effektivitet.

Særlige kvaliteter af CPLDS

CPLD'er adskiller sig gennem deres tilpasningsdygtige programmering, omfattende integration, hurtige udviklingsfunktioner og vidtgående anvendelighed sammen med økonomiske produktionsomkostninger.De appellerer til dem med minimal hardwareoplevelse, der tjener som pålidelige og sikre produkter, der ikke kræver udtømmende test.Som et vidnesbyrd om deres dygtighed i storskala kredsløbsdesign, spiller CPLDS en nøglerolle i prototypeudvikling og serverer kørsler under 10.000 enheder, hvilket udgør en nyttig kompetence for dig.Den adeptness, som CPLDS tilpasser sig til at udvikle projektkrav, tjener dem ofte påskønnelse og understreger deres faktiske alsidighed i dynamiske miljøer.

Applikationsmetoder

Disse integrerede kredsløb giver dig mulighed for at uddybe logiske funktioner, der er skræddersyet til deres behov ved hjælp af både skemaer og hardwarebeskrivelsessprog på udviklingsplatforme.For eksempel er der i design af en telefonsvarer, skemaer og hardwarebeskrivelser forberedt og samlet på en computer.Ved hjælp af et downloadkabel overføres koden til CPLD til programmering i systemet, der omfatter test, fejlfinding og forbedring af design.Med succes udformede design er masseproduceret ved replikering af CPLD-chips.I projekter som trafiklyssystemer bliver gentagelse af designprocessen nødvendigt, svarende til at genopbygge et hus for at gendanne sin nyhed.Denne gentagne metodologi lægger ofte grundlaget for mestring, hvilket øger både færdigheder og selvtillid.

Ledende varianter

Gennem årene har virksomheder som Altera, Gitter og Xilinx afsløret fremtrædende linjer med CPLD'er.Bemærkelsesværdige eksempler inkluderer altera's EPM7128S, Lattice's LC4128Vog Xilinx's XC95108 .Disse modeller har fundet fremtrædende roller på tværs af forskellige globale applikationer.De, der har haft privilegiet at arbejde med disse forskellige produkter, bemærker ofte de subtile, men alligevel kraftige forskelle, der optimerer bestemte funktionaliteter.Dette afspejler en fin udvælgelsesproces påvirket af specifikke projektkrav, hvor hver variant har sin unikke appel.

Identifikation og klassificering af FPGA og CPLD

|

Aspekt |

Cpld |

FPGA |

|

Logisk adfærdsdannelse |

Form logisk opførsel ved hjælp af produktperiode struktur.

Eksempler: Gitter ISPLSI -serien, Xilinx XC9500 -serien, Altera Max7000s

serie, gitter mach -serie |

Form logisk opførsel ved hjælp af en tabelopslagsmetode.

Eksempler: Xilinx Spartan Series, Altera Flex10k, Acex1K -serien |

|

Egnethed |

Velegnet til algoritmer og kombinationslogik, værker

Bedre med begrænsede triggere og rige produktbetingelser |

Velegnet til sekventiel logik fungerer bedre med

Strukturer rig på triggere |

|

Timing forsinkelse |

Kontinuerlig ledningsstruktur giver ensartet og

Forudsigelige timingforsinkelser |

Segmenteret ledningsstruktur fører til uforudsigelig timing

forsinkelser |

|

Programmering af fleksibilitet |

Rettede interne kredsløb ændres til programmering.

Programmering af logisk blokeringsniveau bruges |

Interne ledninger ændres til programmering.Logik

Programmering på gate-niveau giver større fleksibilitet |

|

Integration |

Lavere integration sammenlignet med FPGA |

Højere integration med mere kompleks ledningsstruktur og

Logikimplementering |

|

Brugervenlighed |

Lettere at bruge med programmering via E2PROM eller Fastflash.

Ingen ekstern hukommelseschip er påkrævet |

Kræver ekstern hukommelse for at gemme programmering

information, der fører til mere kompleks brug |

|

Hastighed og forudsigelighed |

Hurtigere hastighed og bedre timing -forudsigelighed på grund af

Klumpet sammenkobling mellem logiske blokke |

Langsommere hastighed og mindre forudsigelig timing på grund af

Programmering og distribueret sammenkobling af gate-niveau |

|

Programmeringsteknologi |

Bruger E2PROM- eller flashhukommelsesprogrammering.Programmeringsdata

opbevares, når systemet er slukket.Understøtter programmering på en

programmerer eller in-system |

Baseret på SRAM -programmering.Programmeringsdata går tabt, når

Systemet er slukket og skal genindlæses.Understøtter dynamisk

Konfiguration |

|

Fortrolighed |

Tilbyder bedre fortrolighed |

Giver lavere fortrolighed |

|

Strømforbrug |

Generelt højere strømforbrug, især med

højere integration |

Lavere strømforbrug sammenlignet med CPLD |

Programmeringssprog for CPLD

Analyse af, hvordan komplekse programmerbare logiske enheder (CPLDS) er programmeret, er en hjørnesten i at udarbejde alsidige hardwareløsninger.De historiske metoder til programmering af CPLD'er har været afhængige af stigediagrammer eller hardwarebeskrivelsessprog (HDL'er), hvor Verilog HDL og VHDL er fremherskende valg.Det valgte sprog kan forme både designstrategien og implementeringseffektiviteten af implementeringer.

• Verilog HDL: Verilog HDL er værdsat for sin enkle syntaks og robuste simuleringsfunktioner, hvilket afspejler de metodologier, der bruges i digital logisk design.Dets integration med Eleconic Design Automation (EDA) -værktøjer giver dig mulighed for problemfrit at udføre syntese og simulering.Den C-lignende syntaks af Verilog er blevet observeret for at sænke adgangsbarrieren for dem med programmering af baggrunde, hvilket fremskynder rejsen fra design til implementering på tværs af en bred vifte af industrisektorer.

• Vhdl: VHDL giver en mere detaljeret og ekspressiv mulighed for HDL -programmering.Det er ofte valget til projekter, der kræver omhyggelig dokumentation og streng type-kontrol, træk, der er værdsat i luftfarts- og forsvarsindustrien.Du kan bemærke, at trods VHDLs potentielle kompleksitet i mindre projekter, understøtter dens disciplinerede struktur oprettelsen af usædvanligt pålidelige design, en nødvendighed i miljøer, hvor sikkerhed er dominerende.

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

NMOS -transistorer: Design, drift og applikationer

på 2024-12-29

The Fast Fourier Transform (FFT): Revolutionering af digital signalbehandling

på 2024-12-29

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-18 147764

-

USB-C pinout og funktioner

på 2000-04-18 111987

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-18 111351

-

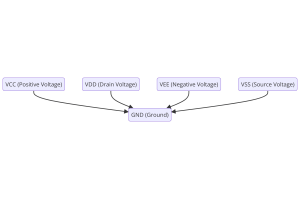

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-18 83751

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79542

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66949

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63091

-

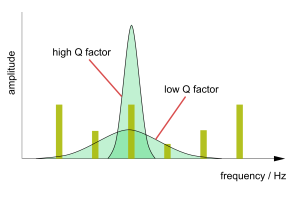

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63028

-

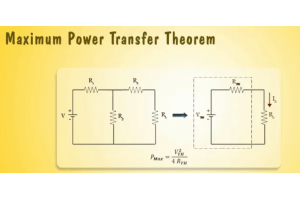

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54092

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52172