Omfattende oversigt over op/ned -tællere: kredsløbsdesign og 74193 IC forklaret

I den komplicerede verden af digital elektronik spiller tællere en vigtig rolle i sekventielt kredsløbsdesign, hvilket muliggør præcis sammenhæng af digitale impulser i forskellige applikationer.Disse basale komponenter drives af flip-flops (FFS) synkroniseret med ur (CLK) -signaler, hvilket sikrer pålidelige tidsmæssige datasporing og -behandling.Uanset om det fungerer som separate enheder eller som basale dele af større systemer, er tællere blevet en krævet i digitalt design.Blandt de forskellige typer tællere skiller op/ned tællere sig ud for deres unikke evne til at tælle i begge retninger og tilbyder enestående fleksibilitet og effektivitet.I denne artikel graver vi ind i mekanikerne, applikationer og betydning af op/ned -tællere med et fokus på den alsidige 74193 IC.Ved at udforske deres rolle i faktiske systemer og digitale innovationer sigter vi mod at give en omfattende guide til dig.Katalog

Forstå op/ned -tælleren

Op/ned-tællere tilbyder en kompliceret tællingsmetode, der giver mulighed for dobbeltretningsoperationer baseret på bestemte kontrolsignaler.Disse tællere findes i applikationer, hvor tæller op og ned er begge nødvendige, som det ses i TTL -teknologier - som 74LS190 og 74LS191 - der adepty switch -tæller som svar på deres indgangsdirektiver.

4-bit binær op/ned tæller

4-bit-tælleren markerer binær tælling, dygtigt navigerer fra 0000 til 1111 og looping cyklisk.Urimpulser driver den stigende mekanisme over en 0-15 rækkevidde, hvor hvert kryds metodisk får en efterfølgende tilstand.

I modsætning hertil er dekrementeringsprocessen, der skifter fra 1111 til 0000, afhængig af fire flip-flops af D-typen aktiveret af urkanter.Den innovative brug af omvendte feedbackmekanismer opnår et harmonisk samspil af output, der fremhæver både kreativitet og præcision.

Synkron 3-bit op/ned-tæller

Den 3-bit synkrone tæller, der bruger JK-flip-flops, eksemplificerer en effektiv tilgang til at tælle fra 0 (000) til 7 (111) og tilbage.Dets synkrone design muliggør raffineret kontrol over tællingsprocessen, hvor hver statsovergang koordineres af præcise inputkommandoer.Denne funktion forbedrer nøjagtigheden i op-tælling fra 0 til 7, mens det dygtigt styrer nedtælling fra 7 tilbage til 0.

Design af et op/ned -tællerkredsløb

3-bit tællerkredsløbet står som et nøgleelement i digitalt design, der serverer forskellige tællings- og timingformål.Det anvender konsekvent flip-flops (FFS) for at bestemme tællingens retning-uenig eller faldende.

I op-tællingstilstand er hver FF på linje med et urindgang hentet fra den foregående FF's output (Q), der styrer kredsløbet i en ordnet opstigning gennem binære tilstande fra 000 til 111. Denne sekvens finder ofte fordel i applikationer, der kræver nøjagtig timingkontrol, inklusive digitale ure og regnemaskiner, hvor nøjagtighed fremkalder tilfredshed og pålidelighed.

At skifte til nedtællingstilstand kræver en smart tilgang, der engagerer flip-flops 'inverse output.Afviger fra en simpel fremadrettet march omdirigerer denne konfiguration hver FF's urindgang til at modtage signaler fra komplementet til den foregående FF's Q -output.Følgelig tæller kredsløbet omvendt, fra binære 111 tilbage til 000. En sådan tilpasningsdygtig funktionalitet viser sig hovedsageligt tiltalende, når man designer reversible tællere til backtracking i systemer som digitale kilomehometers og dekrement -timere - den subtile glæde ved at bevæge sig bagud som glat, som fremadrettet ikke kan overses.

Mekanik i op/ned -tælleren

Funktionaliteten af op/ned -tælleren er afhængig af en kontrolindgang, der definerer dens operationelle tilstand, der dikterer, om tællingen vil stige op eller falde ned.Essensen af dens operation ligger i den sømløse synkronisering mellem output fra flip-flops (FFS) og kontrolsignaler, der påvirker efterfølgende FFS.I applikationer kan selv den mindste afvigelse fra perfekt timing føre til tællingsfejl, idet de understreger, hvor dynamisk det er at koordinere signal -timing nøjagtigt.

• Tællingstilstand

|

Tilstand |

QC |

QB |

Qa |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

2 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

|

4 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

• Count-down-tilstand

|

Tilstand |

QC |

QB |

Qa |

|

7 |

1 |

1 |

1 |

|

6 |

1 |

1 |

0 |

|

5 |

1 |

0 |

1 |

|

4 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

I en typisk konfiguration opbevarer tre flip-flops en 3-bit digital værdi, hvilket muliggør et binært grev, der spænder fra 0 til 7. Du kan ofte stå over for udfordringer, der opretholder pålideligheden af lagrede værdier, især når du beskæftiger sig med miljøer med elektrisk støj eller interferens.For at tackle disse udfordringer anvendes yderligere synkronisering eller filtreringsteknikker ofte, hvilket sikrer, at data bevares med integritet under overgange.

Logikporte påvirker markant, hvordan disse signaler er rettet, hvilket sikrer, at tælleren er i overensstemmelse med dets operationelle behov.De administrerer strømmen for at sikre, at kun en stat - enten forøgelse eller dekrementering - er aktive til enhver tid.Avancerede kredsløb kan inkorporere programmerbar logik, der tilbyder forbedret tilpasningsevne og dynamiske justeringer.Dette introducerer et spændende aspekt: Design af tællere med fremsyn til fremtidig skalerbarhed kan udvide deres anvendelighed markant.

Raffinering af urimpulsdynamik ved hjælp af en op/ned -tæller

En op/ned-tæller transformerer tilstande ved at justere flip-flop (FF) udgange som svar på urimpulsændringer.

• I det op-tællingsscenarie: Tilslut den indledende flip-flop til logik 0, hvilket får det til at skifte med faldende urkanter, hvilket forbedrer synkroniseringen med systemmål for problemfri strømning.Tanker, der stammer fra digitale kredsløbsdesignoplevelser, antyder, at afbalancering af disse skiftende handlinger kan reducere falske triggere og derved øge pålideligheden over tid.

Nedtælling og harmonisk statsovergang

• I nedtællingstilstand: Opret forbindelse til logik 1 for at gøre det muligt for alle flip-flops at skifte, hvilket fører til en jævn reduktion fra højere tilstande.Denne metode kan sammenlignes med den omhyggelige afvikling af en fjeder, hvor præcision og timing sikrer en minimal mekanisk stamme under tilbagevenden til baseline.Dette arrangement letter et gradvis fald, indtil en nulstillingssekvens bliver bedt om.

Effektiv cyklus nulstilling og konsistensforsikring

Rutinemæssige nulstillinger forekommer hvert otte urcyklusser, hvilket sikrer en konsekvent drift.De otte-cyklusrammer tilvejebringer en defineret fase for hvert tilstandsskifte, hvilket sikrer, at hver fase afsluttes effektivt, før den næste begynder.Feedback fra praktiske anvendelser antyder, at disse periodiske nulstillinger forhindrer akkumulerende fejl, hvilket styrker operationel ligevægt.

74193 op/ned tæller IC Oversigt

De 74193 Integreret kredsløb, kendt som en 4-bit synkron binær tæller, administrerer adeptly både opadgående og nedadgående tællingsfunktioner.Dens evne til at håndtere tællingssekvenser op til en modulo på 16 egner sig til en lang række digitale applikationer.Denne IC er unikt designet med terminaler specifikt til op- og nedtælling sammen med en master -nulstilling og belastningsindgang, som giver let at konfigurere den oprindelige tilstand i henhold til forskellige behov.

Arkitekturen i 74193 IC understøtter ubesværet retningsbestemt tælling.I digitale enheder forbedrer valget mellem opadgående og nedadgående tælling systemets tilpasningsevne.Hver tællingsoperation er nøjagtigt på linje med urpulsen, hvilket gør det til et pålideligt valg for komplicerede systemer, hvor timing er af essensen.For dig kan denne synkronisering være en strategisk faktor for at sikre ensartet sekvensudførelse.

En nøglefunktion ved denne IC er master -nulstilling, der giver mulighed for øjeblikkelig nulstilling af alle bits - en funktion, der ofte implementeres under opstart eller når de har rettet fejl.Endvidere øger belastningsindgangen sin brugbarhed ved at give dig mulighed for at indstille forudbestemte indledende tællinger, hvilket tillader en grad af personalisering, der kræves i en række digitale sammenhænge.En sådan personalisering bliver grundlæggende i scenarier, hvor enheder gennemgår regelmæssig initialisering eller kræver særlig håndtering under afbrydelser.

Pin -konfiguration

|

PIN -nummer |

Pin -navn |

Beskrivelse |

|

Pin 1 |

CLR |

En aktiv lav nulstillingsindgang. |

|

Pin 2 |

CLK |

Et urindgangssignal. |

|

Pin 3 |

A (LSB) |

Data forudindstillet input. |

|

Pin 4 |

B |

Data forudindstillet input. |

|

Pin 5 |

C |

Data forudindstillet input. |

|

Pin 6 |

D (MSB) |

Data forudindstillet input. |

|

Pin 7 |

Enp |

En aktivhøj input mærket ENP. |

|

Pin 8 |

GND |

Jordstift. |

|

Pin 9 |

Belastning |

En aktiv lav datalastindgang. |

|

Pin 10 |

Ent |

Et aktivt højt input mærket ent. |

|

Pin 11 |

QD (MSB) |

Flip-flop output. |

|

Pin 12 |

QC |

Flip-flop output. |

|

Pin 13 |

QB |

Flip-flop output. |

|

Pin 14 |

QA (LSB) |

Flip-flop output. |

|

Pin 15 |

RCO |

Ripple udfører output, der overgår fra 0 til 1. |

|

Pin 16 |

VCC |

Power Input Pin. |

Funktioner

|

Funktion |

Beskrivelse |

|

CLK -frekvens |

Fungerer med en CLK -frekvens på 32 MHz. |

|

Strømforbrug |

Strømforbruget er lukket til 93 MW. |

|

Tællertype |

Funktioner som en 4-bit modulo-16 op/ned tæller. |

|

Forudindstillede input |

Leveres med tilgængelige forudindstillede input. |

|

Programmering |

Funktioner synkron programmering. |

|

Ripple bære |

Har en intern krusning bære til effektiv tælling. |

|

Udfør output |

Tilbyder en bæreudgang, der er egnet til N-bit cascading. |

|

Formeringstid |

Kan prale af en forplantningstid på 14 ns. |

Bygning af en op/ned -tæller med IC 74193

Komplekset 74193 IC, der er anerkendt for sine tilpasningsdygtige tællingsfunktioner, er en værdifuld komponent i digitale systemer til at muliggøre alsidige op/nedtællingsopgaver.I kredsløbslayoutet er PIN-16 forbundet til VCC for at give IC operationel effekt.De klare stifter er jordet strategisk, der fungerer til at nulstille tælleren, når det er nødvendigt, hvilket hjælper med at opretholde systemets pålidelighed og ydeevne.

Binære data kommer ind i IC gennem stifter PA, PB, PC og PD.De tilsvarende binære output kan fås adgang til ved QA, QB, QC og QD, der leverer forarbejdede tællinger, der for det meste er fordelagtige for opgaver som timingkredsløb og frekvensdelere, der kræver høj præcision.

Tællingsretningen, hvad enten det drejer sig om stigning eller dekrementering, styres gennem specialiserede urindgange.Denne kapacitet giver dig mulighed for dynamisk at justere tællingssekvensen af IC, hvilket forbedrer dens fleksibilitet i forskellige applikationer.Når du bruger IC i praktiske scenarier, er det dominerende at omhyggeligt forme urpulsen og adressere støjproblemer for at undgå forkerte tællinger, hvilket sikrer, at kredsløbet fungerer pålideligt.

Sammenlignende analyse af tæller og ned tæller

|

Op til tæller |

Ned tæller |

|

Up -tælleren stemmer fra '0' til sin maksimale grænse |

Dun -tælleren starter fra dens topværdi og falder ned

til '0' |

|

Det tæller begivenheder i en stigende rækkefølge |

Det tæller begivenheder i en faldende rækkefølge |

Styrker og begrænsninger af op/ned tællere

Styrker

Op/ned -tællere giver en række fordele, især i verden af Integrering i højhastighedssystemer.Deres ligefremme flip-flop-struktur hjælper med ubesværet forbindelse, hvilket ofte fører til omkostningseffektive muligheder for digitale enheder, hvor minimering af kompleksitet er en prioritet. Evnen til at tælle i begge retninger - opad og nedad - adds alsidighed, hvilket viser sig at være gavnlige i applikationer som digitale ure eller begivenhedstællere, hvor tovejsoptælling er ønskelig. Derudover skinner deres funktionalitet i testsystemer, der bruges til at bekræfte logiske signaler.Hands-on applikationer sætter pris på deres Ukompliceret design, hvilket sikrer enklere fejlfinding og vedligeholdelse, der giver en bemærkelsesværdig fordel for dig, der fokuserer på problemløsnings- og optimeringsopgaver.

Begrænsninger

På trods af styrkerne viser op/ned -tællere bestemte begrænsninger, især vedrørende præcision ved forhøjede frekvenser. Når operationelle hastigheder stiger, kan de støde på unøjagtigheder og udgøre udfordringer i systemer, der prioriterer høj pålidelighed. Disse unøjagtigheder stammer ofte fra afhængighed af ekstern ursynkronisering, som specifikt kan Kræv supplerende flip-flop kredsløb.Sådanne krav kan Forøg kredsløbskompleksiteten og introducer potentielle timingforsinkelser.Når man administrerer komplicerede bit -systemer, er der desuden Eventuelle forsinkelser, der er forbundet med tællerne, kan forværrepåvirker den samlede systemydelse.Derfor kan du ofte udforske alternative løsninger eller yderligere komponenter til at afbøde disse effekter og basere deres strategier på forbedrede synkroniseringsteknikker.At navigere i disse kompromiser kræver en tankevækkende evaluering af systembehov, og hvordan sådanne elementer kan påvirke ydeevnen, og ofte styrer du dig mod strategiske designforbedringer, der er skræddersyet til specifikke applikationskrav.

Anvendelser af op/ned tællere

Auto-reverserende tællere

I en verden af systemteknik, der kræver omhyggelig kontrol, introducerer op/ned -tællere en nyttig funktion: den automatiske justering af tællingsretningen ved indstillede grænser.Denne tilpasningsevne understøtter en fejlfri overgang mellem fremad og bagudtælling.En sådan funktion bliver især værdsat i automatiserede miljøer, hvor sporing af bevægelse i begge retninger dybt påvirker driftseffektiviteten.Industriel robotik udnytter for eksempel denne attribut for at sikre nøjagtighed efter at have nået deres bevægelsesgrænser.

Urdelere

Inden for digitale elektroniske systemer bidrager op/ned -tællere væsentligt til fremstilling af urdelere, som i stand til at modulere hyppigheden af ursignaler.Denne modulation hjælper med at konstruere timingsignaler, der er nøglen til at drive forskellige komponenter ved forskellige frekvenser inden for et integreret system.Ved at tilbyde ure med forskellige hastigheder spiller disse tællere en vigtig rolle i synkronisering af forskellige processer og tilfredsstiller derved unikke systembehov.

Parkeringsstyringssystemer

I byområder, der er kvalt med trafik, leverer op/ned -tællere dynamiske løsninger gennem parkeringsstyringssystemer.Ved metodisk at øge tællingen med hvert køretøjs indgang og reducere det ved udgang giver disse tællere rettidige opdateringer på tilgængelige parkeringspladser.Denne faktiske sporingsmekanisme understøtter effektiv udnyttelse af parkeringsinfrastruktur, mens du beriger din oplevelse.

Frekvensopdeling

For opgaver, der involverer frekvensopdeling i kommunikationsnetværk, viser op/ned -tællere at være usædvanligt fordelagtige på grund af deres lave støj og reduceret strømforbrug.Disse tællere hjælper med den omhyggelige opdeling og styring af frekvenser, hvilket muliggør indkvartering af flere kanaler inden for et netværk.I miljøer med omfattende signalbehandling sikrer brugen af sådanne tællere minimal interferens, opretholdelse af integriteten og kvaliteten af kommunikationssignaler.

Asynkron decadal tælling

Op/ned tællere muliggør asynkron dekadal tælling, der bruges til applikationer, hvor operationer forekommer uafhængigt af globale ure.I asynkrone systemer giver disse tællere en pålidelig tilgang til at opnå base-10-tælling, der udmærker sig i tilpasningsevne uden at fortabe præcision.Deres værktøj skinner i systemer, der opererer på tværs af forskellige forhold, og justerer jævnt uden at ofre nøjagtighed.

Konklusion

Denne artikel graver sig ind i de komplicerede design og operationelle aspekter af op/ned -tælleren med fokus på 74193 IC.Kendt for sine dobbelte tællingsfunktioner - både stigende og faldende - har det forskellige applikationer, fra sofistikerede parkeringssystemer til komplicerede frekvensopgaver.Når teknologiske landskaber skifter, kan en dyb forståelse af disse komponenter skabe innovation og øge effektiviteten.Up/ned -tællerens nytte strækker sig ud over konventionelle applikationer og vove sig ind i automatiserede systemer, hvor præcise tællingsmekanismer øger effektiviteten.I dynamiske trafikstyringsløsninger spiller sådanne tællere for eksempel en vigtig rolle ved at integrere faktiske data for at optimere flow.Udnyttelse af enhedens alsidighed gør det muligt at udfordre udfordringer i forskellige sektorer med tilpassede strategier.Fra branchespecifikke indsigter kan den nøjagtige implementering af disse tællere markant øge systemets ydelse.

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Hvad er teorien bag en 8-bit op/ned-tæller?

En 8-bit op/ned-tæller håndterer et 8-bit digitalt signal, hvilket viser sig at være nyttigt i designarkitekturer såsom digital-til-analog-konvertere (DAC'er) og dekodere.Det indeholder ofte LED -skærme og involverer konfiguration gennem otte stifter.Tællerens tilpasningsevne fremhæves ved at udforske digital signalbehandling vanskeligheder, der er nyttige i både sofistikerede beregningssystemer og enklere enheder.Implementering af disse tællere kræver typisk omhyggelig opmærksomhed på signalintegritet og opsætning af nuancer.

2. hvordan bruger en op/ned-tæller JK-flip-flops?

Denne 4-bit tæller anvender synkron operation med JK-flip-flops for at ændre tællingsretning baseret på den logiske tilstand af op/ned-indgangen.Det reagerer på urimpulser, mens de aktiverende input fungerer som en aktiv kontrolmekanisme.Du kan udnytte dette design for at sikre pålidelig timing og sekventiel ydelse i forskellige applikationer, hvilket illustrerer effektiviteten af synkrone digitale systemer.At forstå disse sofistikerede systemer kan tilbyde bredere indsigt i digitale kredsløb og inspirere til innovative logiske designløsninger.

3. Hvad adskiller 74192 -tælleren fra 74193 -tælleren?

74192 fungerer som en BCD-årtiskæller, og 74193 fungerer som en 4-bit synkron binær tæller.Begge er skræddersyet til forskellige roller inden for digital elektronik.Anerkendelse af hver tællers forskellige funktioner hjælper med at vælge passende komponenter til synkrone tællingsopgaver.Sådanne designbeslutninger kan væsentligt påvirke driftseffektiviteten og sammenhængen i komplekse kredsløb, hvilket tilbyder værdifulde perspektiver til optimering af integreret systemdesign.

4. Hvordan defineres en 2-bit op/ned-tæller?

En 2-bit op/ned-tæller gennemgår en simpel binær sekvens fra 0 til 3, der fungerer i både opadgående og nedadgående ordrer.Denne operation fremhæver de ultimative logiske principper og den enkelhed, der er mulig i digitale systemer.Sådanne tællere tjener som klare eksempler på binær aritmetik, der tilbyder praktiske læringsoplevelser, der forbedrer uddannelsesmodeller og letter enhedstest og uddyber således forståelsen af binære operationer.

5. Hvordan fungerer CD4029 -modfunktionen?

CD4029 -tælleren fungerer fleksibelt, der er i stand til binær og årti -tælling.Det forudindstilles via marmeladeindgange efter modtagelse af et højt aktivt signal og nulstilles til nul, når lavt aktiver er aktiveret.Denne tilpasningsevne understøtter applikationer, der kræver præcise signalbehandlingskonfigurationer.Praktisk viden om dens drift sikrer, at CD4029 glat kan håndtere nulstillinger og mode -overgange, hvilket afspejler en omfattende forståelse af kontroldynamik i digitale kredsløb.

Den ultimative guide til SX1262 -chipmodulet

på 2024-11-29

Omfattende sammenligning: LM324 vs LM358 operationelle forstærkere

på 2024-11-28

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-18 147760

-

USB-C pinout og funktioner

på 2000-04-18 111967

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-18 111351

-

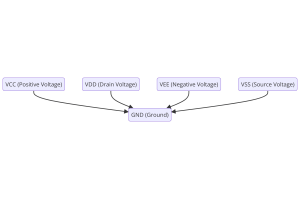

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-18 83729

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79516

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66930

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63078

-

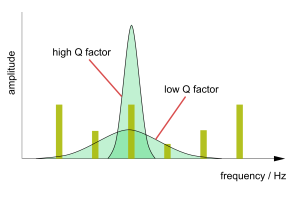

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63023

-

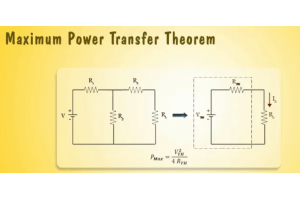

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54088

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52160