EP1C4F400C8 FPGA: Funktioner, specifikationer, programmering og alternativer

Hvis du arbejder med programmerbar logik, giver EP1C4F400C8 dig en praktisk balance mellem ydeevne og omkostninger.I denne artikel lærer du, hvad denne FPGA er, dens nøglefunktioner som logisk kapacitet, hukommelse og I/O -indstillinger, og hvordan dens struktur understøtter pålidelig design.Du vil også se dens specifikationer, applikationer i systemer, programmeringsproces og hvordan den sammenlignes med lignende dele.Katalog

Hvad er EP1C4F400C8?

De EP1C4F400C8 er medlem af Intels (tidligere Altera's) Cyclone FPGA-familie, designet som en omkostningseffektiv og pålidelig programmerbar logisk løsning.Denne enhed er bygget på en 0,13 um SRAM-proces og tilbyder moderat logikdensitet og fleksible I/O-indstillinger inden for en kompakt FBGA-400-pakke.Cyclone -familien, der inkluderer enheder som EP1C3, EP1C6, EP1C12 og EP1C20, blev oprettet for at afbalancere ydeevne og overkommelige priser for skalerbare design, hvilket tillader let migration mellem densitetsniveauer og pakker.Kendt for stabilitet og bred adoption er det stadig et betroet valg i ældre design.

Leder du efter EP1C4F400C8?Kontakt os for at kontrollere den aktuelle lager, ledetid og prisfastsættelse.

EP1C4F400C8 CAD -modeller

EP1C4F400C8 Symbol

EP1C4F400C8 Fodaftryk

EP1C4F400C8 3D -model

EP1C4F400C8 -funktioner

• Logisk kapacitet

EP1C4F400C8 tilbyder omkring 4.000 logiske elementer, der er organiseret i 400 logiske array -blokke (laboratorier).Dette gør det velegnet til mellemklasse-design, der kræver moderat logikdensitet og samtidig opretholder omkostningseffektiviteten.

• Indlejret hukommelse

Det integrerer cirka 76,5 kbits indlejret hukommelse.Denne interne RAM understøtter databuffering, opbevaring og små hukommelsesfunktioner, hvilket reducerer behovet for eksterne hukommelseskomponenter i mange designs.

• Høj I/O -tælling

Enheden leverer 301 brugerkonfigurerbare I/O-stifter i sin 400-ball FBGA-pakke.Denne høje pin -tælling muliggør rig forbindelse for komplekse systemer, der kræver flere perifere grænseflader.

• Bred I/O -standarder understøtter

Det understøtter flere I/O-standarder, herunder LVTTL, LVCMOS, SSTL-2, SSTL-3 og differentielle LVD'er.Denne fleksibilitet giver FPGA mulighed for at interface direkte med en række moderne logikfamilier og hukommelsesenheder.

• Højhastighedsdifferentiel signalering

Med LVDS -understøttelse op til 640 Mbps håndterer FPGA hurtige krav til dataoverførsel.Dette gør det praktisk til applikationer såsom højhastighedskommunikationsforbindelser og hurtige digitale grænseflader.

• Urstyring med PLL'er

Chip integrerer to faselåste sløjfer (PLL'er) og otte globale urnetværk.Disse funktioner tillader præcis urgenerering, multiplikation og jitterkontrol til timingkritiske applikationer.

• Kerneoperation med lav spænding

Ved at operere med en nominel 1,5 V kernesspænding balanserer enheden ydelsen med lavere strømforbrug.Dette spændingsniveau blev optimeret til 0,13 um CMOS-teknologien anvendt i dens fabrikation.

• Fleksible I/O -spændinger

FPGA understøtter I/O -spændinger på 1,5 V, 1,8 V, 2,5 V og 3,3 V på forskellige banker.Denne alsidighed gør det muligt for den at interface med både arv og moderne systemkomponenter.

• SRAM-baseret konfiguration

Som andre Cyclone FPGA'er er det SRAM-baseret og kræver rekonfiguration ved enhver power-up.Dette giver fleksibilitet til opdateringer, men nødvendiggør også en ekstern konfigurationsenhed eller controller.

• Bitstream -komprimeringsstøtte

EP1C4F400C8 understøtter komprimerede bitstream -belastning under konfiguration.Dette reducerer de eksterne hukommelseskrav og fremskynder konfigurationstider.

• PCI -overholdelse

Det inkluderer indbygget support til PCI-standarder (33/66 MHz, 32/64-bit).Denne funktion gør det muligt at integrere enheden direkte i systemer, der kræver PCI -grænseflade uden yderligere brodannelse af logik.

Cyklonlaboratoriestruktur

Diagrammet viser den logiske array -blok (LAB) -struktur, der anvendes i cyklon -FPGA'er som EP1C4F400C8.Hvert laboratorium opretter forbindelse til et netværk af sammenkoblinger: række sammenkoblinger, søjleforbindelser og lokale sammenkoblinger, som rute signalerer mellem logiske elementer og andre blokke.Direkte link-sammenkoblinger giver hurtige stier med lav latens til tilstødende laboratorier, hvilket forbedrer timingens ydelse i signalstier.Denne arkitektur er vigtig, fordi den afbalancerer routingfleksibilitet med effektivitet, hvilket gør det muligt for FPGA at håndtere komplekse design, mens den holder hastighed og areal optimeret.

Cyclone I/O Banks Diagram

Diagrammet illustrerer I/O -bankstrukturen af cyklon -FPGA'er såsom EP1C4F400C8.Enheden er opdelt i fire I/O -banker, der hver er drevet af sin egen forsyningsbus, hvilket tillader at blande forskellige spændingsstandarder inden for en enkelt FPGA.Alle banker støtter en lang række I/O-standarder, herunder LVTTL, LVCMO'er, LVD'er, RSD'er og SSTL, mens Banks 1 og 3 også understøtter 3,3-V PCI til kompatibilitet med ældre systemer.Denne fleksible I/O -arkitektur er vigtig, fordi den muliggør problemfri integration med forskellige eksterne enheder og grænseflader, hvilket gør FPGA tilpasning til forskellige applikationer.

EP1C4F400C8 -specifikationer

|

Type |

Parameter |

|

Fabrikant |

Altera/Intel |

|

Serie |

Cyclone® |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Antal laboratorier/CLB'er |

400 |

|

Antal logiske elementer/celler |

4000 |

|

Samlede rambits |

78.336 |

|

Antal I/O. |

301 |

|

Spænding - Forsyning |

1.425V ~ 1.575V |

|

Monteringstype |

Overflademontering |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Pakke / sag |

400-BGA |

|

Leverandørenhedspakke |

400-fbga (21 × 21) |

|

Basisproduktnummer |

EP1C4 |

EP1C4F400C8 -applikationer

1. Digital Signal Processing (DSP)

EP1C4F400C8 kan programmeres til at udføre opgaver såsom filtrering, FFT'er og signalmodulation.Dens kombination af logiske elementer og indlejret hukommelse gør det velegnet til højhastighedsbehandling.Dette gør det muligt for det at erstatte traditionelle DSP -chips med en fleksibel FPGA -løsning, der kan omprogrammeres til forskellige algoritmer.

2. Indbyggede og kontrolsystemer

I industrielle og indlejrede systemer bruges denne FPGA ofte til at implementere brugerdefinerede controllere, sequencere og tilstandsmaskiner.Dens rekonfigurerbare logik giver mulighed for at skræddersy hardwareadfærd netop til systembehov.Ved at integrere kontrollogik inde i FPGA reduceres antallet af eksterne komponenter, hvilket forbedrer pålideligheden og sænkningsomkostningerne.

3. kommunikation og interface brodannelse

Enheden understøtter flere I/O -standarder og kan fungere som en bro mellem forskellige kommunikationsprotokoller.Det bruges ofte til at forbinde PCI, LVDS, SDRAM og andre grænseflader problemfrit inden for et system.Dette gør det meget nyttigt i netværksudstyr, indlejrede controllere og arv-til-moderne interface-konverteringer.

4. dataindsamling og behandling

Med høj I/O-tilgængelighed og fleksibel hukommelse er EP1C4F400C8 velegnet til dataindsamlingssystemer.Det kan direkte interface med ADC'er og sensorer, behandle dataene i tide og forberede dem til opbevaring eller transmission.Sådanne applikationer er almindelige i medicinske instrumenter, testudstyr og videnskabelige måleenheder.

EP1C4F400C8 lignende dele

|

Specifikation |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Fabrikant |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

FPGA -familie |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

|

Logiske elementer (LES) |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

|

Indlejret hukommelse (BITS) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

I/O -stifter |

301 |

301 |

301 |

301 |

249 |

97 |

|

Pakke / sag |

400-fbga |

400-fbga |

400-fbga |

400-fbga |

324-fbga |

144-tqfp |

|

Hastighedskvalitet |

C8 |

C8 |

C8 |

C6 (hurtigere) |

C8 |

C8 |

|

Kerne spænding |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

|

Driftstemp.Rækkevidde |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C.

|

EP1C4F400C8 -programmeringstrin

Før du kan bruge EP1C4F400C8 FPGA, skal du indlæse dit design på enheden.Programmering involverer konfiguration af FPGA med en bitstream -fil, så den ved, hvordan man opfører sig som dit tilsigtede kredsløb.

1. Vælg konfigurationsskema og indstil MSEL -stifter

Du begynder med at vælge konfigurationsskemaet, der bedst passer til din opsætning, såsom aktiv seriel, passiv seriel eller JTAG.Dette gøres ved at indstille MSEL-stifterne til specifikke logiske niveauer inden power-up.Hver tilstand bruger forskellige stifter og protokoller, så du skal bekræfte kompatibilitet med dine designværktøjer og konfigurationshukommelse.At tage det rigtige valg her sikrer en jævn konfigurationsproces.

2. Anvend strøm og initialiser enheden

Tænd derefter FPGAs kerne og I/O -skinner inden for de specificerede spændingsområder.Under opstart skal du holde NConfig -pinen lav for at holde enheden i nulstilling, indtil forsyningsspændingerne er stabile.Når den er stabil, frigiver du nulstilling, og enheden signaliserer beredskab ved at køre nstatus -pin.Dette garanterer, at FPGA er korrekt initialiseret, før konfigurationen begynder.

3. Overfør konfigurationsbitstream

På dette tidspunkt sender du konfigurationsdatafilen (Bitstream) til FPGA ved hjælp af dit valgte skema.I aktiv seriel eller passiv seriel tilstand kommer bitstream fra en ekstern hukommelsesenhed, mens JTAG tillader direkte programmering via kabel.Enheden læser kontinuerligt i konfigurationsdataene, indtil den er afsluttet.Din designsoftware genererer denne bitstream for at matche dine logiske krav.

4. Bekræft vellykket konfiguration (conf_done)

Når FPGA er færdig med indlæsningen, hævder den Conf_Done PIN for at vise, at konfigurationsdata blev modtaget med succes.På samme tid udfører enheden intern initialisering, såsom clearingregistre og aktivering af I/O.Hvis Conf_Done ikke går højt, betyder det normalt, at konfigurationsdataene eller opsætningen har en fejl.At se denne pin er den enkleste måde at verificere, at processen er komplet.

5. Udfør valgfri rekonfiguration i systemet

Endelig har du muligheden for at opdatere eller omprogrammere FPGA uden at fjerne den fra bestyrelsen.Ved hjælp af JTAG eller en indlejret controller kan du indlæse en ny bitstream direkte, hvilket er nyttigt til firmwareopdateringer.Denne fleksibilitet giver dig mulighed for at ændre, debug eller opgradere dit system, selv efter implementering.Det sikrer, at dit FPGA-baserede design kan tilpasse sig over tid til ændrede krav.

EP1C4F400C8 Fordele og ulemper

Fordele

• Omkostningseffektivt valg til mellemklasse design

• Høj I/O -antal sammenlignet med lignende densitetsenheder

• Fleksibel spænding og I/O -standardstøtte

• Støttet af modne værktøjer og dokumentation

• Brug af lavere effekt end ældre FPGA -generationer

Ulemper

• Forældet med begrænset langsigtet tilgængelighed

• Nedre logik og hukommelseskapacitet vs. moderne FPGA'er

• langsommere driftshastighed og I/O -ydeevne

• Kræver ekstern hukommelse til konfiguration på power-up

• Mangler avancerede funktioner som DSP-blokke og højhastighedstransceivere

EP1C4F400C8 Emballagedimensioner

|

Type |

Parameter |

|

Pakningstype |

FBGA (Fine-Pitch Ball Grid Array) |

|

Boldtælling |

400 |

|

Ball Pitch (E) |

1,0 mm (typisk for Cyclone EP1C4F400) |

|

Kuglediameter (b) |

0,45 mm (nominel) |

|

Pakningstørrelse (D × E) |

21 mm × 21 mm |

|

Pakkehøjde (a) |

2,40 mm (max) |

|

Substrattykkelse (A2) |

~ 0,40 mm |

|

Skimmelhætttykkelse (A3) |

~ 1,90 mm |

|

Kuglehøjde (A1) |

0,25 mm (nominel) |

|

Pin A1 hjørne |

Markeret til orientering |

|

Array -layout |

20 × 20 gitter (med hjørne kugler mangler) |

|

Montering |

Surface Mount (SMD) |

EP1C4F400C8 Producent

EP1C4F400C8 blev oprindeligt fremstillet af Altera Corporation, en pioner inden for programmerbare logiske enheder og FPGA -teknologi.I 2015 blev Altera erhvervet af Intel Corporation, og produktlinien blev en del af Intels Programmerbare Solutions Group (PSG).I dag støtter Intel disse Legacy Altera -enheder, mens de fokuserer på udvikling på nyere FPGA -familier, hvilket sikrer kontinuitet for eksisterende brugere og fremmer innovation inden for programmerbar logik.

Konklusion

EP1C4F400C8 skiller sig ud som en omkostningseffektiv og alsidig FPGA, der tilbyder solid ydelse til mellemklasse-design.Med sine 4.000 logiske elementer, indlejret hukommelse, omfattende I/O -support og kompatibilitet med flere spændings- og interface -standarder, giver den fleksibilitet på tværs af forskellige applikationer.Dens arkitektur, programmeringsproces og bred anvendelighed i DSP, indlejrede systemer og dataindsamling gør det til et praktisk valg på trods af dens arvestatus.Mens det mangler avancerede funktioner, der findes i nyere enheder og står over for begrænset langsigtet tilgængelighed, er det stadig en pålidelig mulighed, der søger gennemprøvede løsninger i skalerbare FPGA-design.

Datablad PDF

EP1C4F400C8 DATASARASS:

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Hvilke værktøjer kræves for at programmere EP1C4F400C8?

Du har brug for Intels Quartus-software (tidligere Altera Quartus II) sammen med et understøttet programmeringskabel såsom USB-Blaster.Disse værktøjer giver dig mulighed for at oprette bitstream og indlæse det i FPGA.

2. kan EP1C4F400C8 håndtere PCI -applikationer direkte?

Ja, det har indbygget overholdelse af PCI-standarder (33/66 MHz, 32/64-bit), hvilket gør det velegnet til PCI-baseret systemintegration uden at kræve ekstra brodannende logik.

3. Hvad sker der, hvis EP1C4F400C8 mislykkes under konfigurationen?

Hvis konfigurationen mislykkes, hævder conf_done -pin ikke højt.Dette peger normalt på en fejl i bitstream -filen, spændingssekventering eller pin -opsætning og skal kontrolleres i din designstrøm.

4. kan EP1C4F400C8 -interface direkte med DDR -hukommelse?

Det understøtter flere I/O -standarder, men har ikke native DDR -grænseflader som moderne FPGA'er.Yderligere designovervejelser eller brodannende komponenter kan være nødvendige.

5. Hvordan sammenlignes EP1C4F400C8 med nyere FPGA'er?

Sammenlignet med moderne enheder har EP1C4F400C8 lavere hastighed, mindre logisk densitet og færre avancerede funktioner.Det er dog stadig et omkostningseffektivt valg for stabile, mellemklasse design, hvor avanceret ydeevne ikke er påkrævet.

EPM3256AFC256-7 CPLD Oversigt: Funktioner, pinout, programmering og applikationer

på 2025-10-03

ADG432BR Analog switch IC: Specifikationer, pinout, alternativer og datablad

på 2025-10-02

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-17 147712

-

USB-C pinout og funktioner

på 2000-04-17 111686

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-17 111315

-

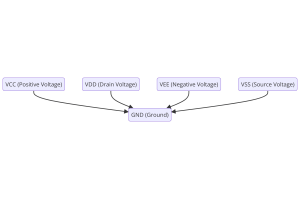

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-17 83585

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79229

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66753

-

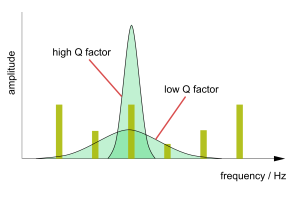

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 62927

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 62801

-

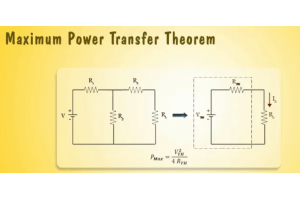

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54024

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 51954