EPF6016ATC144-2N FPGA: Funktioner, programmering, applikationer og alternativer

Denne vejledning handler om EPF6016ATC144-2N, en type chip kaldet en FPGA.Det bruges i digitale systemer, der skal være fleksible og let at opdatere.Guiden forklarer, hvad chippen gør, hvordan den fungerer, dens hoveddele og funktioner, hvordan man bruger og programmerer den, hvor den kan bruges, og hvorfor den stadig er et godt valg i dag.Katalog

Hvad er EPF6016ATC144-2N?

De EPF6016ATC144-2N er medlem af Flex 6000 FPGA -familien udviklet af Altera, nu en del af Intel.Denne enhed er bygget på SRAM-baseret omprogrammerbar logik og er konstrueret til fleksibilitet i digitale logiske applikationer i midten af densitet.Det udnytter Optiflex-arkitekturen, der kombinerer logiske array-blokke (laboratorier) og en højhastighedsinterconnect-matrix for at levere effektiv ressourceudnyttelse og hurtig signalruting.EPF6016ATC144-2N understøtter rekonfiguration i systemet, hvilket gør det ideelt til design, der kræver opdateringer eller ændringer efter implementering.Som en del af Flex 6000-serien tilbyder den en omkostningseffektiv løsning til udskiftning af traditionelle portarrays, samtidig med at udviklingscyklussen forenkler.

Leder du efter EPF6016ATC144-2N?Kontakt os for at kontrollere den aktuelle lager, ledetid og prisfastsættelse.

EPF6016ATC144-2N CAD-modeller

EPF6016ATC144-2N Symbol

EPF6016ATC144-2N Fodaftryk

EPF6016ATC144-2N 3D-model

EPF6016ATC144-2N-funktioner

• Logisk kapacitet

EPF6016ATC144-2N tilbyder omkring 16.000 systemporte, implementeret ved hjælp af 1.320 logiske elementer (LES) på tværs af 132 logiske array-blokke (laboratorier).Dette giver moderat kompleksitet, der er egnet til Mid-Range FPGA-applikationer.

• I/O -stifter

Det understøtter op til 117 brugerkonfigurerbare I/O-stifter.Disse stifter muliggør fleksibel forbindelse til forskellige systemkomponenter og eksterne enheder.

• Kerne spænding

Kernen fungerer ved 3,3V med et funktionelt interval fra 3,0V til 3,6V. Dette tillader kompatibilitet med standard lavspændings digitale systemer.

• I/O -spænding

Dens multivolt I/O -funktion understøtter grænseflade med enheder ved hjælp af 3,3V eller 2,5V niveauer.Dette forenkler integration i blandede spændingsmiljøer.

• Driftstemperatur

Standard driftsforbindelsestemperaturområdet er 0 ° C til +85 ° C.Dette understøtter typiske kommercielle og industrielle miljøer.

• Forsyningsstrøm

Det trækker cirka 5 mA under normal drift og mindre end 0,5 mA i standbytilstand.Dette hjælper med at bevare strømmen i energibevidste design.

• Urhastighed (hastighedskvalitet –2n)

Med en –2 hastighedskvalitet opnår det interne logiske frekvenser op til ca. 166 MHz.Dette muliggør hurtig beregning i signalbehandling eller kontrollogik.

• Arkitektur

Baseret på Alteras Optiflex-arkitektur bruger den LUT-baseret logik med dedikerede routingressourcer.Denne arkitektur tilbyder høj logikdensitet og effektiv ydelse.

• FastTrack Interconnect

FastTrack Routing Grid muliggør signalstier med lav latens-signal og understøtter højhastighedsdataoverførsler på tværs af logiske blokke.Dette bidrager til konsekvent timing og ydeevne.

• Konfiguration i kredsløb

Den bruger SRAM-baseret logikkonfiguration, hvilket gør det muligt for FPGA at blive omprogrammeret i systemet.Dette understøtter designopdateringer eller dynamisk hardware -tilpasning uden fjernelse.

• JTAG -grænsescanning

Enheden inkluderer IEEE 1149.1-kompatibel JTAG-grænse-scanningslogik.Dette letter debugging og testbarhed i systemet af tavler og sammenkoblinger.

• Hot-Socketing support

Det kan indsættes eller fjernes sikkert, mens den drives i 3,3V -systemer.Denne funktion er nyttig i modulære eller servicerbare hardwareplatforme.

• Funktionel test

Hver enhed testes fuldt funktionelt inden afsendelse.Dette sikrer kvalitet og eliminerer behovet for brugerdefinerede testvektorer under udvikling.

• PCI -kompatibilitet

Enheden er kompatibel med PCI Local Bus Revision 2.2 for 5V drift.Dette gør det muligt at bruge det i Legacy PCI-baserede indlejrede systemer.

Optiflex Arkitekturblokdiagram

Diagrammet viser, hvordan de interne dele af FPGA er organiseret og tilsluttet.I midten er logiske array -blokke (laboratorier), dette er de vigtigste bygningsenheder på chippen.Hvert laboratorium indeholder flere logiske elementer (LES), der udfører de grundlæggende digitale operationer, såsom logiske porte og flip-flops.Labs er forbundet med en lokal sammenkobling, der gør det muligt for logikken inde i hver blok mulighed for at arbejde effektivt sammen.For bredere kommunikation på tværs af chippen forbinder laboratorierne til række og kolonne FastTrack -forbindelser, hurtige signalveje, der lader data bevæge sig hurtigt fra den ene del af chippen til en anden med lav forsinkelse.Omkring de ydre kanter af diagrammet er input/outputelementerne (IOE).Disse forbinder FPGAs interne logik til eksterne enheder ved at konvertere mellem chipens logiske niveauer og de spændingsniveauer, der bruges af anden hardware.Dette layout med sine modulære blokke og højhastighedsrutningsstier afspejler den fleksibilitet og ydeevnefokus for Optiflex-arkitekturen.

Flex 6000 timingmodel

Flex 6000 timingmodel viser, hvordan signaler bevæger sig og er forsinket, når de rejser gennem FPGA.I midten af modellen er logiske elementer (LES), hvilke procesdata og kontrolsignaler med specifik timing.Hver LE forbindes til timingstier som T_DATA_TO_REG og T_REG_TO_OUT, som definerer, hvor lang tid det tager for signaler at komme ind, behandles og forlade logikken.

Ved siden af LES er der specielle stier kaldet Lab Carry og Lab Cascade.Disse giver signaler mulighed for at bevæge sig vandret mellem logiske elementer i den samme blok, hvilket understøtter hurtige operationer som tilføjelser og sammenligninger.Disse stier har også deres egne timingværdier, såsom T_CARRY_TO_REG og T_CASC_TO_OUT, for at måle forsinkelser under disse operationer.

I bunden af diagrammet håndterer input/outputelementerne (IOES) signaler, der går ind og ud af chippen.De inkluderer forsinkelsespunkter som T_IN_DELAY, der tegner sig for variationer, når de modtager data fra eksterne enheder.

Modellen inkluderer også routingstier på forskellige niveauer (T_LOCAL, T_ROW, T_COL og T_GLOBAL), der hver repræsenterer, hvor langt et signal rejser, og hvor meget tid det tager.Disse stier hjælper med at forstå og styre forsinkelser på tværs af forskellige dele af chippen, hvilket gør det lettere at opfylde ydeevne og timingmål.

EPF6016ATC144-2N-specifikationer

|

Type |

Parameter |

|

Fabrikant |

Altera/Intel |

|

Serie |

Flex 6000 |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Antal laboratorier/CLB'er |

132 |

|

Antal logiske elementer/celler |

1320 |

|

Antal I/O. |

117 |

|

Antal porte |

16000 |

|

Spænding - Forsyning |

3V ~ 3.6V |

|

Monteringstype |

Overflademontering |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Pakke / sag |

144-LQFP |

|

Leverandørenhedspakke |

144-tqfp (20x20) |

|

Basisproduktnummer |

EPF6016 |

EPF6016ATC144-2N applikationer

1. Digital Signal Processing (DSP) opgaver

Med 1.320 logiske elementer og hurtig sammenkobling understøtter EPF6016ATC144-2N implementeringen af små til mellemklasse digitale signalbehandlingsfunktioner.Det kan bruges til at oprette brugerdefinerede FIR -filtre, FFT -kerner eller parallel aritmetisk logik til signaltransformation.Selvom det mangler dedikerede DSP-blokke eller indlejrede multiplikatorer, kan dens generelle logik håndtere gentagne multiplicerede multiplicerede operationer, der er egnede til indlejret lydbehandling, sensordatafiltrering og bølgeformformning i kontrol- eller kommunikationssystemer.

2. Indlejret kontrol og industriel automatisering

Enheden er velegnet til indlejrede kontrolapplikationer i industrielle miljøer.Dens evne til at interface med blandet spænding I/O (2,5 V og 3,3 V), dens stabile drift under standard kommercielle temperaturer (0–85 ° C), og support til hot-spoting gør det pålideligt til integration i programmerbare logiske controllere (PLC'er), motorstyringsenheder, instrumenteringsgrænseflader og generel-rulle automatiseringsudstyr.Rekonfigurabiliteten giver mulighed for langsigtet produktfleksibilitet, hvor logik kan opdateres uden at udskifte hardware.

3. Kommunikationsprotokolbro og interface -logik

Takket være dets multivolt I/O-support og effektive routingnetværk kan EPF6016ATC144-2N bruges til at implementere brugerdefinerede kommunikationsgrænseflader og protokolkonvertere.Det kan bygge UARTS, SPI -controllere eller parallelle busoversættere for at muliggøre interaktion mellem uoverensstemmende digitale systemer.Dens moderate I/O-antal (117 GPIO'er) og intern urstyring understøtter også tidsfølsom signalering, hvilket gør det velegnet til netværksudstyr, arvbussemulering eller som et limlogisk element i større datakommunikationssystemer.

4. Bestyringsniveau test, fejlsøgning og validering

Med indbygget JTAG-grænse-scanningsevne (IEEE 1149.1-kompatibel) understøtter EPF6016ATC144-2N avanceret bestyrelsesniveau-test uden at kræve eksterne logiske sonder eller påtrængende diagnostik.Det kan verificere I/O-forbindelse, registrere åbne eller kortslutninger og udføre kontrol i systemet under produktion eller feltvedligeholdelse.Denne funktion er nyttig i komplekse flerlags PCB eller i systemer, hvor traditionel adgang til testpunkter er begrænset eller upraktisk.

EPF6016ATC144-2N lignende dele

|

Funktioner |

EPF6016ATC100-1 |

EPF6016ATC100-3N |

EPF6016ATC144-3N |

|

Fabrikant |

Altera |

Intel (Altera Legacy) |

Intel (Altera Legacy) |

|

Familie |

Flex 6000 |

Flex 6000 |

Flex 6000 |

|

Logiske elementer (LES) |

1.320 |

1.320 |

1.320 |

|

Gate Count (ca. |

16.000 |

16.000 |

16.000 |

|

Pakke |

100-PIN TQFP |

100-PIN TQFP |

144-PIN TQFP |

|

Bruger I/O -stifter |

81 |

81 |

117 |

|

Hastighedskvalitet |

-1 (standard) |

-3n (høj hastighed) |

-3n (høj hastighed) |

|

Maks. Urfrekvens |

Lavere (typisk ~ 100 MHz) |

Højere (op til ~ 166 MHz) |

Højere (op til ~ 166 MHz) |

|

Konfigurationstype |

SRAM-baseret |

SRAM-baseret |

SRAM-baseret |

|

Strømforsyningsspænding |

3.3 v |

3.3 v |

3.3 v |

|

Hot-hocketing |

Ja |

Ja |

Ja |

|

JTAG/grænsescanning |

Ja |

Ja |

Ja |

|

Applikationer |

Grundlæggende logik, kompakte design |

Hurtigere kontrollogik, kompakt |

Systemer med høj ydeevne, mere I/O |

|

Tilgængelighed |

Forældet |

Forældet |

Forældet |

EPF6016ATC144-2N programmeringstrin

1. Vælg konfigurationstilstand

EPF6016ATC144-2N understøtter SRAM-baseret konfiguration, hvilket betyder, at den kræver programmering på enhver power-up.Enheden giver mulighed for flere konfigurationsskemaer, oftest passiv seriel (PS) og passiv parallel asynkron (PPA).Konfigurationstilstand bestemmes af, hvordan MSEL -pin er tilsluttet.For eksempel, når MSEL er bundet lavt, forventer enheden, at data sendes serielt via ekstern EEPROM (såsom EPC1) eller et downloadkabel.Valg af den korrekte konfigurationsmetode afhænger af systemdesignet, EEPROM-baseret til automatisk opstart eller kabelbaseret til prototype og test.

2. Sammenlign FPGA -designet og generere en programmeringsfil

For at programmere FPGA skal du først oprette dit hardware -design ved hjælp af Intels Quartus eller Legacy Max+Plus II -designsoftware.Efter kompilering genererer værktøjet en SOF (SRAM -objektfil), der repræsenterer den konfigurerede logik.Denne SOF skal derefter konverteres til et format, der er kompatibelt med din valgte konfigurationsmetode:

• .RBF eller .POF for EEPROM -enheder (f.eks. EPC1).

• .ttf eller .hex til mikrokontroller eller parallel belastning.

Konverteringen udføres ved hjælp af det indbyggede filkonverterværktøj i designsoftwaren.Dette trin sikrer, at bitstream formateres korrekt for FPGA at fortolke.

3. Program konfigurationshukommelsen (hvis du bruger EEPROM)

I applikationer, hvor en seriel konfigurationsenhed som en EPC1 bruges, er det næste trin at indlæse konfigurationsdata i EEPROM.Dette gøres typisk ved hjælp af et desktop -programmeringsværktøj (f.eks. Max+Plus II -programmør eller quartus -programmør).Processen involverer at placere EEPROM i en programmeringsstik eller tilslutte den i kredsløb, indlæse den relevante programmeringsfil (normalt .POF eller .RBF) og indlede programcyklussen.Når EEPROM først er programmeret, leverer automatisk konfigurationsdata til FPGA, hver gang systemet driver op, hvilket eliminerer behovet for manuel omprogrammering.

4. Konfigurer ved hjælp af et downloadkabel (passiv seriel)

Et alternativ til EEPROM-baseret boot-up bruger et downloadkabel (såsom USB-Blaster eller ByteBlaster) til direkte at konfigurere FPGA.I denne metode forbinder du kablet til din pc og FPGA's NConfig, DCLK, Data og Conf_Done Pins.Ved hjælp af Quartus -programmøren starter du konfigurationsprocessen, der pulserer nconfig lav for at begynde.Værktøjet sender derefter konfigurationsdata serielt gennem datalinjen, klokket af DCLK.Processen er afsluttet, når Conf_Done går høj, hvilket indikerer en vellykket konfiguration og enhedens overgang til brugertilstand.

5. Konfigurer ved hjælp af en mikrokontroller (passiv seriel/parallel)

Hvis dit system bruger en indlejret mikrokontroller, kan det også fungere som FPGAs konfigurationsmaster.I denne opsætning hævder mikrokontrolleren NConfig lav til at nulstille FPGA og skifter derefter konfigurationsbitstream gennem data, mens DCLK skifter DCLK.Timingkrav skal respekteres, datasætningstid før uret og hold tid bagefter er god til vellykket konfiguration.Mikrokontrolleren kan overvåge nstatus- og conf_done -stifterne for at detektere konfigurationsfejl eller bekræfte vellykket færdiggørelse.Denne metode tilbyder fuld kontrol over konfigurationsprocessen og understøtter dynamiske opdateringer på området.

6. Overvåg konfigurationssignaler

Under konfigurationsprocessen giver FPGA feedback gennem statusstifter:

• nstatus angiver fejldetektion;Det går lavt, hvis der opstår en fejl (f.eks. CRC -fejl eller overtrædelse af timing).

• Conf_Done går højt, når alle konfigurationsbits er indlæst og verificeret med succes.

Hvis nstatus forbliver høj og conf_done-overgange højt i slutningen af sekvensen, indtaster enheden automatisk brugertilstand, hvor brugerdefineret logik bliver aktiv.Denne signalovervågning er vigtig for at sikre, at programmeringsprocessen afsluttes med succes.

7. Udfør rekonfiguration, når det er nødvendigt

Fordi EPF6016ATC144-2N er SRAM-baseret, kan den konfigureres til enhver tid ved at skifte NConfig-pin Low, der nulstiller enheden og genstarter konfigurationscyklussen.Denne funktion giver mulighed for fleksible systemopdateringer og ændringer under drift uden fysisk udskiftning.Evnen til at rekonfigurere, mens in-kredsløb også understøtter redundans, dynamisk funktionsswapping eller korrigerer fejl efter installationen.Dette gør enheden meget velegnet til applikationer, der kræver tilpasningsevne eller lang levetid.

8. Overhold timing og elektriske krav

Programmering af EPF6016ATC144-2N kræver også opmærksomhed på elektriske og timingbegrænsninger.Konfigurationsuret (DCLK) skal opfylde frekvensgrænser (f.eks. Typisk op til 10 MHz i standard serielle tilstande).Enheden kræver en kort forsinkelse (ca. 200 ms) efter power-up til den interne nulstilling for at stabilisere sig.Derudover skal alle konfigurationssignaler være rene, støjfrie og korrekt afsluttet.Hvis du bruger hot-socketing, skal man sørge for at sikre signalintegritet og korrekt sekventering af effekt og I/O.

EPF6016ATC144-2N fordele

• Omkostningseffektivt til midtkompleksitetsdesign

EPF6016ATC144-2N sætter en balance mellem overkommelige priser og funktionalitet, hvilket gør den ideel til design, der kræver mere fleksibilitet end fast logik, men ikke retfærdiggøre udgifterne eller strømmen over hovedet for avancerede FPGA'er.

• Forenklet PCB -design og integration

Sammenlignet med FPGA'er med højere densitet, der ofte kræver Fine-pitch BGA-pakker, kommer EPF6016ATC144-2N i en standard 144-polet TQFP-pakke.Denne emballage forenkler både design og fremstilling af PCB'er, fordi det undgår behovet for avancerede layoutværktøjer, mikrovier eller dyre højlagsbestyrelser.Det letter også håndopløsning eller grundlæggende omarbejdning, hvilket er gavnligt for mindre hold eller laboratorier med begrænsede samlingskapaciteter.

• Lav risiko for forældelse under implementering

På grund af sin mangeårige støtte i ældre industrielle applikationer forbliver EPF6016ATC144-2N tilgængelig på mange sekundære markeder og understøttes stadig bredt i designsoftware som Quartus II og MAX+PLUS II.For virksomheder, der opretholder lang-lifecycle-produkter, såsom fabriksautomation, målesystemer eller telekommoduler, sikrer dette fortsat adgang til kendt godt silicium uden behov for at redesigne hardware omkring nyere, mere komplekse FPGA'er.

• Pålidelig opførsel

I modsætning til nogle nyere højtydende FPGA'er, der fungerer i stramme marginer og er følsomme over for effekt og temperatursvingninger, er EPF6016ATC144-2N robust og tolerant over for almindelige miljøvariationer.Det fungerer komfortabelt på tværs af det kommercielle temperaturområde og understøtter hot-hocketing, hvilket gør det pålideligt i modulære eller brugbare systemer.Denne pålidelighed gør det til et praktisk valg for systemer, der kræver ensartet ydelse over tid og under variable forhold.

• Langsigtet designstabilitet

I scenarier, hvor langvarig tilgængelighed og designfrysning er vigtigere end avanceret ydeevne, er denne enhed en solid kandidat.Når logikken er valideret, og konfigurationsfilen låst ned, kan hele systemet forblive uændret i årevis, endda årtier.Dette er en stor fordel i rumfarts-, transport- og militære applikationer, hvor rekvalificering af nye dele er dyre eller upraktiske.

EPF6016ATC144-2N Emballagedimensioner

Pakningstype: TQFP-144 (tynd quad flad pakke)

Kropsstørrelse: 20 mm × 20 mm

Pin tonehøjde: 0,5 mm

Pin -tælling: 144 stifter

Pakkehøjde: 1,0 mm

LEADRAMME TYPE: Gull-Wing fører på alle fire sider

Monteringstype: Overflademontering (SMT)

EPF6016ATC144-2N Producent

EPF6016ATC144-2N blev oprindeligt fremstillet af Altera Corporation, en pioner inden for udviklingen af feltprogrammerbare portarrays (FPGA'er).I 2015 blev Altera erhvervet af Intel Corporation, og enheden er nu officielt noteret under Intels programmerbare løsningsgruppe, der administrerer og understøtter Alteras arv FPGA -produktlinjer.Selvom EPF6016ATC144-2N er en del af en ophørt familie, er Intel fortsat den formelle producent og depot for denne enhed og opretholder dokumentation, arkiveret support og livscyklusmeddelelser under Intel-branding.

Konklusion

EPF6016ATC144-2N er en fleksibel og pålidelig FPGA for mange forskellige projekter.Det tilbyder en god mængde logikkraft, mange input/output-stifter og lette opdateringer i systemet.Dets design understøtter blandede spændingssystemer, hurtige datavevægelse og omprogrammering uden at fjerne det fra et bord.Det bruges ofte i ting som kontrolsystemer, signalbehandling, kommunikationslink og testudstyr.Med stærk støtte, lang tilgængelighed og enkel emballage er det stadig et smart valg, der har brug for en omkostningseffektiv og stabil løsning.

Datablad PDF

EPF6016ATC144-2N Datablad:

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Hvilke værktøjer skal jeg programmere EPF6016ATC144-2N i dag?

Du kan bruge Intels Legacy Quartus II eller MAX+Plus II -software til udvikling og kompilering.Til programmering forbliver værktøjer som USB-Blaster-kablet og Quartus-programmøren kompatible til konfiguration.

2. er EPF6016ATC144-2N velegnet til små produktionsløb eller prototype?

Ja.Dens TQFP-144-pakke gør det nemt at prototype uden behov for avancerede monteringsværktøjer.Det er også ideelt til produktion af små skala, hvor der er behov for lave omkostninger og fleksibilitet.

3. hvordan sammenligner EPF6016ATC144-2N med nyere FPGA'er med hensyn til ydeevne?

Selvom den ikke er så funktionsrige som moderne high-end FPGA'er, tilbyder EPF6016ATC144-2N pålidelig ydelse for moderat logisk kompleksitet med lavere strømforbrug og enklere integration, hvilket gør det omkostningseffektivt for mange applikationer.

4. Er det sikkert at hot-plug EPF6016ATC144-2N i live-systemer?

Ja.Denne FPGA understøtter hot-hocketing til 3,3V-systemer, så den kan indsættes eller fjernes uden at tænde for værtsbestyrelsen, ideel til feltservice eller modulopbyggede hardwaredesign.

5. Hvorfor skal jeg vælge EPF6016ATC144-2N over brugerdefinerede ASIC- eller CPLD-løsninger?

EPF6016ATC144-2N tilbyder hurtigere udviklingscyklusser, omprogrammering af felt og reducerede omkostninger på forhånd sammenlignet med ASICS.Sammenlignet med CPLD'er giver det mere logisk kapacitet og fleksibel routing, ideel til skalerbare og udviklende design.

LC5768MC-75F256C CPLD: Funktioner, specifikationer, fordele og applikationer

på 2025-07-10

Kom godt i gang med MC7447AHX1000NB

på 2025-07-10

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-18 147778

-

USB-C pinout og funktioner

på 2000-04-18 112033

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-18 111352

-

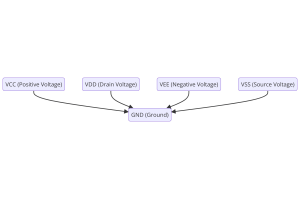

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-18 83790

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79596

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66975

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63110

-

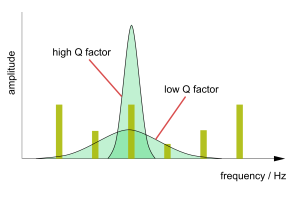

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63043

-

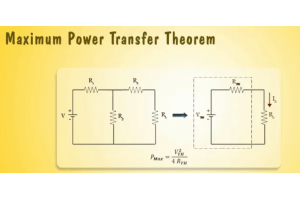

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52197