EPF8820ARC208-4 FPGA Guide: Funktioner, arkitektur, applikationer og programmering

Denne artikel handler om EPF8820ARC208-4, en speciel chip, der bruges i elektronik.Det forklarer, hvad chippen gør, hvordan den fungerer, og hvor den kan bruges.Du lærer om dens dele, hvordan man indstiller det op, og hvorfor bruge det stadig i dag i ting som radioer, maskiner, biler og mere.Det viser også, hvordan det sammenlignes med andre lignende chips.Katalog

Hvad er EPF8820ARC208-4?

De EPF8820ARC208-4 er en arv FPGA -enhed fra Flex 8000 -serien udviklet af Altera, nu under Intel Programmerbar Solutions Group.Designet ved hjælp af en CMOS SRAM-baseret arkitektur hører den til en familie af rekonfigurerbare logiske enheder, der markerede en fase i programmerbar logikudvikling.Flex 8000-serien blev anerkendt for sin alsidige logiske cellestruktur og skalerbar sammenkobling, der var egnet til generel digital integration.EPF8820ARC208-4 falder specifikt i en variant i midten af hastighed inden for denne serie og sammenkoblingsfunktioner.Den deler sin arkitektur med andre varianter af hastighedskvalitet, såsom ‑2, -3 og -5, der primært adskiller sig i timing-ydelsen.

Leder du efter EPF8820ARC208-4?Kontakt os for at kontrollere den aktuelle lager, ledetid og prisfastsættelse.

EPF8820ARC208-4 Funktioner

• Flex 8000 Arkitektur

EPF8820ARC208-4 er bygget på Altera's Flex 8000-arkitektur, der bruger SRAM-baseret konfiguration til programmerbarhed i systemet.Det tilvejebringer en omkostningseffektiv og fleksibel løsning til mellemstore logikdensitetsapplikationer.

• Logikdensitet

Denne enhed integrerer 672 logiske elementer og leverer cirka 8.000 brugbare systemporte.Det tilbyder en passende balance mellem kompleksitet og ydeevne til indlejret kontrol, limlogik og statsmaskinedesign.

• 5V kerne med Multivolt ™ I/O -support

Betjening på en 5V -forsyning understøtter enheden også 3,3V og 5V I/O -standarder ved hjælp af Multivolt ™ I/O -teknologi.Dette gør det tilpasningsdygtigt til blandede spændingssystemer og arv-grænseflade.

• Regrammerbar konfiguration i kredsløb

EPF8820ARC208-4 er SRAM-baseret og understøtter konfiguration i kredsløb ved hjælp af eksterne serielle eller parallelle proms.Det giver mulighed for hurtige designopdateringer og rekonfiguration uden at fjerne enheden fra kredsløbet.

• FastTrack Interconnect Routing

Dens FastTrack-interconnect-struktur giver et forudsigeligt routingstof med høj hastighed.Denne arkitektur understøtter effektiv logikplacering og timingkontrol, hvilket muliggør strømlinet designydelse.

• Bær og kaskadekæder til aritmetik

Dedikerede bær- og kaskadekæder forbedrer implementeringen af aritmetiske funktioner som tilføjere og tællere.Disse funktioner reducerer logisk forsinkelse og forenkler konstruktionen af komplekse matematikoperationer.

• PCI Bus Compliance (Rev 2.2)

Denne enhed overholder PCI Local Bus Specification Revision 2.2, hvilket gør den velegnet til brug i PCI-baserede systemer.Det understøtter 5V-tolerante PCI-signalmiljøer.

• JTAG Boundary Scan Support

EPF8820ARC208-4 inkluderer indbyggede IEEE 1149.1 (JTAG) grænse-scanningsfunktioner.Dette letter debugging, brættestning og verifikation i systemet uden at kræve yderligere kredsløb.

• Programmerbar Slew Rate Control

Dens outputdrivere har programmerbar dræbningshastighedskontrol, hvilket hjælper med at minimere skiftestøj.Dette er fordelagtigt i højhastighedsdesign til signalintegritet.

• Standbytilstand med lav effekt

Enheden er designet til effektive effektivitet og forbruger mindre end 0,5 mA i standbytilstand.Dette gør det muligt for systemer at spare strøm i tomgang eller inaktive perioder.

• Driftstemperatur: 0 ° C til 70 ° C

Komponenten fungerer pålideligt inden for et kommercielt temperaturområde fra 0 ° C til 70 ° C.Det er ideelt til brug af generel formål i kontrollerede miljøer.

Flex 8000 blokdiagram

Diagrammet illustrerer den interne struktur, og hvordan FPGA behandler logik og forbindelser.I midten er Logic Array Blocks (LABS), der indeholder flere logiske elementer (LES).Disse LE'er er programmerbare og kan konfigureres til at udføre en lang række logiske opgaver, der understøtter både kombination og sekventiel design.Denne fleksibilitet giver mulighed for brugerdefineret implementering af digital kredsløb.

Omkring laboratorierne er I/O -elementerne (IOE), der håndterer kommunikation mellem FPGA og eksterne enheder.De understøtter input-, output- og tovejssignaler, mens de imødekommer forskellige spændingsniveauer.Tilslutning af alle dele er FastTrack Interconnect, et højhastighedsrutesystem, der forbinder laboratorier og IOE'er effektivt.Denne opsætning sikrer hurtig dataoverførsel, glat signalruting og pålidelig ydelse på tværs af forskellige applikationer inden for Flex 8000 -serien.

Flex 8000 timing -tilstand

Diagrammet fremhæver, hvordan forsinkelser påvirker logisk behandling og signalstrøm inden for FPGA.Inde i hvert logisk element (LE) bestemmer timingfaktorer som opslagstabel (LUT) forsinkelse, bærer kædeforsinkelse og registeropsætning/holdtider, hvor hurtigt logiske operationer reagerer på inputændringer.Disse interne forsinkelser er vigtige for at opretholde nøjagtig og stabil drift, især i hurtigskiftkredsløb.

For I/O -operationer viser timingtilstand, hvordan signaler opfører sig, når de kommer ind og afslutter FPGA.Nøglepunkter inkluderer outputforsinkelse samt inputopsætning og holdtider, der definerer, hvor længe eksterne signaler skal være stabile til korrekt datafangst.Diagrammet skitserer også forsinkelser mellem tilsluttede LE'er, herunder bær- og kaskadestier, der påvirker strømmen af logik på tværs af enheden.I alt sikrer disse timingelementer synkroniserede, pålidelige ydelse på tværs af Flex 8000's arkitektur.

Flex 8000 bærekæde drift

Bærekæden i EPF8820ARC208-4 Flex 8000 er designet til at udføre hurtige aritmetiske beregninger ved at forbinde flere logiske elementer (LES) sammen.Hver LE indeholder en opslagstabel (LUT), et bærelogikkredsløb og et register.Processen starter med et indføresignal, der kommer ind i den første LE (LE1), der sammen med input A1 og B1 producerer et sum-output (S1) og et bæresignal.

Dette bæresignal overføres derefter direkte til den næste LE i kæden (LE2, LE3, og så videre), hvilket giver hver LE mulighed for at beregne sin egen sum output (S2 til SN) ved hjælp af dens input og den indkommende bære.Den sidste LE i sekvensen genererer det endelige udførelsessignal og afslutter operationen.Denne bærekædestruktur muliggør hurtig, effektiv tilføjelse, ideel til opbygning af tilføjere, tællere og anden aritmetisk-baseret logik i Flex 8000-arkitekturen.

EPF8820ARC208-4-specifikationer

|

Type |

Parameter |

|

Fabrikant |

Altera/Intel |

|

Serie |

Flex 8000 |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Antal laboratorier/CLB'er |

84 |

|

Antal logiske elementer/celler |

672 |

|

Antal I/O. |

152 |

|

Antal porte |

8000 |

|

Spænding - Forsyning |

4,75V ~ 5,25V |

|

Monteringstype |

Overflademontering |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Pakke / sag |

208-BFQFP Exposed Pad |

|

Leverandørenhedspakke |

208-RQFP (28x28) |

EPF8820ARC208-4 applikationer

1. Digital Signal Processing (DSP) og datasåkontrol

EPF8820ARC208-4 er velegnet til implementering af brugerdefinerede DSP-funktioner på grund af dens moderate logikdensitet og effektive routingarkitektur.Det kan håndtere datas-vejmanipulation til operationer såsom filtrering, modulation og transformation af højhastigheds digitale signaler.

2. Brugerdefineret busgrænseflade og coprocessor offloading

Med sit store antal I/O -stifter og Multivolt ™ -støtte bruges denne FPGA ofte til at designe brugerdefinerede perifere grænseflader eller bro uforenelige logiske niveauer.Det tjener også som en co-processor, der offlader gentagne kontrol- eller databehandlingsopgaver fra hovedprocessoren.

3. Softwaredefineret radio- og kommunikationsbehandling

Enhedens fleksibilitet og evne til at blive omprogrammeret gør det ideelt til applikationer som software-defineret radio (SDR), hvor moduleringsordninger eller protokoller kan ændre sig.Det kan dynamisk håndtere kodning, afkodning og signalstyring på tværs af kommunikationslag.

4. ASIC Prototyping og hardwareemulering

EPF8820ARC208-4 anvendes ofte i prototypefasen af ASIC-udvikling.Dens omprogrammerbare arkitektur tillader hurtig validering, test og timing -simulering af komplekse digitale design, før de forpligter sig til silicium.

5. Stemmegenkendelse og krypteringsmotorer

Denne FPGA er i stand til at implementere medium-kompleksitetslogik som stemmegenkendelsesrørledninger og kryptografiske algoritmer.Tilstedeværelsen af bærekæder og registreret I/OS sikrer hurtig beregning og lav-latenssignalbehandling, der kræves til sådanne applikationer.

6. Industrielle kontrol- og instrumenteringssystemer

Den forudsigelige timing, store fanout -synkrone kontroller og fleksible logiske blokke gør denne FPGA velegnet til industrielle automatiseringssystemer.Det bruges ofte i programmerbar timing, statsmaskinkontrol og signalkonditioneringskredsløb.

7. Aerospace and Defense Indbyggede systemer

Denne enhed bruges i rumfarts- og forsvarselektronik, hvor der er behov for konfigurationsfleksibilitet og pålidelig drift i kontrollerede miljøer.Det understøtter sikker firmwarebelastning og tilbyder lav standby-strøm, der gavner missionskritiske applikationer.

8. Automotive elektroniske moduler

I Automotive Electronics kan EPF8820ARC208-4 findes i kontrolmoduler, der håndterer logikoversættelse, diagnostik eller datagaggregering mellem sensorer og centrale ECU'er.Dens rekonfigurerbare karakter tillader opdateringer og forbedringer, selv efter implementering.

9. Telekommunikationsskift og protokolhåndtering

I telekomsystemer understøtter denne FPGA skiftelogik, protokolhåndtering og timingstyring.Det kan tilpasse sig forskellige signalstandarder og sikre kompatibilitet og opgraderbarhed i dynamiske kommunikationsnetværk.

EPF8820ARC208-4 lignende dele

Her er en sammenligningstabel over EPF8820ARC208-4 og dens mest relevante lignende dele fra den samme Flex8000-familie:

|

Delnummer |

Hastighedskvalitet |

Pakningstype |

I/O -stifter |

Logiske elementer |

Temperaturklasse |

|

EPF8820ARC208-4 |

–4 (baseline) |

208-PIN QFP |

152 |

672 |

Kommerciel |

|

EPF8820ARC208-2 |

–2 (langsommere) |

208-PIN QFP |

152 |

672 |

Kommerciel (0–70 ° C) |

|

EPF8820ARC208-3 |

–3 (medium) |

208-PIN QFP |

152 |

672 |

Kommerciel |

|

EPF8820ARC208-5 |

–5 (hurtigere) |

208-PIN QFP |

152 |

672 |

Kommerciel |

|

EPF8820AQC208-4 |

–4 |

208-PIN QFP (AQC) |

152 |

672 |

Kommerciel |

|

EPF8820ARI208-4H |

–4 |

208-PIN QFP |

152 |

672 |

Industriel (–40–85 ° C) |

EPF8820ARC208-4 Programmeringstrin

1. Generer konfigurationsfil

Start med at oprette konfigurationsfilen ved hjælp af Altera's udviklingssoftware såsom Max+Plus II eller Quartus.Denne fil, typisk omkring 16 kb i størrelse, indeholder den komplette bitstream, der er nødvendig for at definere logikken og routing af EPF8820ARC208-4.

2. Vælg konfigurationsskema

Vælg en passende konfigurationsmetode baseret på systemkrav: Enten aktiv seriel/parallel (hvor FPGA kontrollerer belastning) eller passiv seriel/parallel (hvor en ekstern controller håndterer konfiguration).Passive metoder er ideelle til systemer, der kræver omprogrammering eller dynamiske opdateringer.

3. Opret hardwareforbindelser

Tilslut de nødvendige konfigurationslinjer såsom NConfig, Conf_Done, DCLK og Data0 mellem FPGA og din valgte konfigurationshukommelsesenhed (f.eks. EPC1, EPC1213).Sørg for, at pull-up-modstande og urkilder er konfigureret korrekt til at matche den valgte konfigurationstilstand.

4. Power-on-initialisering

Når systemet driver op eller nconfig hævdes, indtaster FPGA konfigurationstilstand og placerer alt I/OS i en tri-state tilstand.Enheden er nu klar til at acceptere konfigurationsdataene baseret på ledningsskemaet, du implementerede.

5. Indlæs konfigurationsdata

I aktiv tilstand henter FPGA data direkte fra EPROM ved hjælp af sin interne oscillator.I passiv tilstand leverer en værtsprocessor eller konfigurationskontroller dataene, og processen afsluttes, når Conf_Done -signalet går højt.

6. Intern initialisering og overgang til brugertilstand

Når bitstream er fuldt belastet, og conf_done hævdes, udfører FPGA intern initialisering, sætter registre og muliggør bruger I/O.Enheden begynder derefter at udføre det logiske design, der er programmeret til den.

7. Valgfri rekonfiguration

Du kan udløse en rekonfigurationscyklus ved at trække NConfig Low, der nulstiller enheden og indtaster konfigurationstilstand igen.Dette giver mulighed for hurtige opdateringer i systemet eller opsving af nedfaldende logik, med hele omprogrammeringsprocessen, der typisk er afsluttet i under 100 millisekunder.

EPF8820ARC208-4 Fordele

• Afbalanceret valg af hastighedskvalitet

EPF8820ARC208-4 tilbyder en ideel balance mellem ydeevne og omkostninger, hvilket gør den hurtigere end lavere kvalitet –2 eller –3 varianter, samtidig med at man undgår det højere prispunkt for –5-hastighedskvaliteten.Dette gør det muligt at imødekomme timingkrav uden for meget betaler for ubrugt lofthøjde.

• Forudsigelige routingforsinkelser til kontrollogik

Takket være sin finkornede vandrette routing og konsistente forsinkelsesstier giver EPF8820ARC208-4 fremragende timing-forudsigelighed.Dette er nyttigt til kontrolorienterede eller statsmaskin-tunge design

• Hurtigtekonfiguration i feltet

Dens SRAM-baserede struktur tillader rekonfiguration på mindre end 100 millisekunder, hvilket muliggør firmwareopdateringer og tilbagefaldslogik i live-systemer.Dette er værdifuldt i fjerntliggende eller missionskritiske applikationer, hvor nedetid skal minimeres.

• Omkostningseffektiv

For applikationer, der kræver omkring 8.000 systemporte, giver EPF8820ARC208-4 den rigtige mængde logik uden overhead af større moderne FPGA'er.Dette holder BOM -omkostninger lave, mens de opfylder funktionalitetskrav.

• Forenklet blandet spændingsintegration

Med indbygget support til både 3,3V og 5V I/O-signalering forenkler enheden systemdesign, når der er grænseflade med ældre TTL- eller blandet spændingskomponenter.Dette eliminerer behovet for yderligere niveauskiftere, sparer bestyrelsesplads og omkostninger.

EPF8820ARC208-4 Emballagedimensioner

• Pakningstype: 208-polet RQFP (rektangulær quad flad pakke)

• Kropsstørrelse (D × E): 30,60 mm × 30,60 mm

• Pakkeoversigt (D1 × E1): ca. 28,00 mm × 28,00 mm

• Bly tonehøjde (e): 0,50 mm

• Blylængde (L): 0,60 mm typisk (rækkevidde: 0,45 mm til 0,75 mm)

• Ledbredde (b): 0,17 mm typisk (rækkevidde: 0,17 mm til 0,27 mm)

• Fører vinkel: 0 ° til 8 °

• Monteringstype: Overflademontering

EPF8820ARC208-4 Producent

EPF8820ARC208-4 er fremstillet af Altera Corporation, et banebrydende firma inden for programmerbare logiske enheder (PLDS) og feltprogrammerbare gatearrays (FPGA'er).Altera udviklede oprindeligt Flex 8000-familien, som denne enhed hører til, og tilbyder en rekonfigurerbar arkitektur, der er skræddersyet til midt-densitets logiske applikationer.I 2015 blev Altera erhvervet af Intel Corporation, og produktet blev fortsat understøttet under Intels programmerbare løsningsgruppe.I 2024–2025 genoprettede Intel imidlertid Altera som et selvstændigt brand, hvilket bekræfter sit fokus på FPGA-udvikling og langvarig støtte.Mens EPF8820ARC208-4 officielt er klassificeret som forældet, forbliver dens fremstillingsarv bundet til Alteras arv med at levere pålidelige, fleksible og vidt vedtagne programmerbare logiske løsninger.

Konklusion

EPF8820ARC208-4 er en fleksibel og pålidelig chip, der tilbyder en god blanding af hastighed, funktioner og omkostninger.Det fungerer godt i mange forskellige systemer, fordi det kan omprogrammeres, understøtter forskellige spændinger og håndterer matematik- og kontrolopgaver hurtigt.Dens design hjælper med at sikre, at signaler bevæger sig glat og nøjagtigt.Selvom det nu betragtes som en ældre eller ophørt del, er det stadig nyttigt i systemer, der har brug for stabil ydelse og ikke let kan skifte til nyere chips.Dette gør det til en smart mulighed for opdateringer, reparationer eller langvarig støtte fra ældre elektronik.

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. kræver EPF8820ARC208-4 ekstern konfigurationshukommelse for at starte op?

Ja, det bruger eksterne serielle eller parallelle PROM'er som EPC1 eller EPC1213 til at indlæse konfigurationsdata under systeminitialisering eller nulstilling.

2. Hvordan ved jeg, om mit eksisterende bestyrelsesdesign understøtter EPF8820ARC208-4-konfigurationstilstand?

Kontroller din skematiske for krævede stifter som NConfig, Conf_Done, DCLK og Data0.Sørg også for, at din konfigurationshukommelse (som EPC1 eller EPC1213) matcher den valgte serielle eller parallelle konfigurationsmetode.

3. kan jeg udføre delvis rekonfiguration på EPF8820ARC208-4?

Nej, EPF8820ARC208-4 understøtter ikke delvis rekonfiguration.Eventuelle opdateringer eller logiske ændringer kræver en fuld bitstream -genindlæsning via standardkonfigurationscyklussen.

4. er der nogen risiko for bitstream-korruption under power-up?

Ja, hvis konfigurationstiming eller signalintegritet ikke opretholdes korrekt, kan der forekomme bitstream -korruption.Sørg for ren effektsekventering og korrekt afkobling i nærheden af FPGA og konfigurationslinjerne.

5. Kan jeg bruge EPF8820ARC208-4 til kryptografiske funktioner eller sikker behandling?

Selvom den ikke er sikkerhedshærdet, er enheden velegnet til implementering af brugerdefinerede kryptografiske logik som grundlæggende krypteringsmotorer eller nøglehåndtering, men den mangler indbyggede sikre funktioner, der findes i moderne FPGA'er.

Hvordan EPM7064AEFC100-10 kan forenkle dit logiske design

på 2025-07-14

LC5768MC-75F256C CPLD: Funktioner, specifikationer, fordele og applikationer

på 2025-07-10

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-18 147778

-

USB-C pinout og funktioner

på 2000-04-18 112023

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-18 111351

-

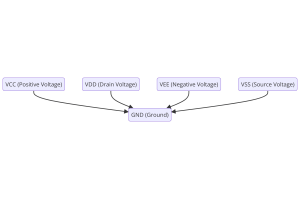

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-18 83777

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79577

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66966

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63105

-

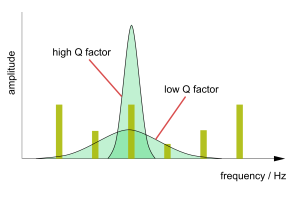

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63041

-

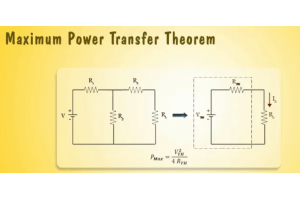

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52190