EPM7064STC100-7 CPLD: Funktioner, applikationer og programmeringsvejledning i systemet

EPM7064STC100-7 er en kraftfuld chip fra Intels MAX® 7000S-serie, designet til at håndtere komplekse opgaver på elektroniske enheder.Denne guide diskuterer de vigtigste funktioner og anvendelser af EPM7064STC100-7, der understreger dens evne til let at blive omprogrammeret, dens hurtige drift og dets fleksible design.Ideel til mange forskellige teknologier, fra små gadgets til store industrimaskiner, er denne chip et vigtigt stykke til at opbygge avancerede digitale kredsløb.Katalog

EPM7064STC100-7 Beskrivelse

De EPM7064STC100-7 er en kompleks programmerbar logikenhed (CPLD) fra Intels MAX® 7000S -serie.Det har 64 makroceller og 1.250 porte, som hjælper med at opbygge komplekse digitale kredsløb.Denne chip kører med en maksimal hastighed på 166,7 MHz med en signalforsinkelse på 7,5 nanosekunder (NS).Det har 68 input/output (I/O) stifter, der fungerer med 3,3V og 5V logik, hvilket gør det nemt at bruge i forskellige kredsløb.En nøglefunktion er dens 5,0V in-system-programmerbarhed (ISP) gennem en JTAG-grænseflade (IEEE 1149.1).Dette betyder, at du kan omprogrammere det uden at fjerne det fra kredsløbet, gøre test og opdateringer lettere.Det kommer i en 100-polet tynd quad flad pack (TQFP), som er en kompakt, overflademonteringspakke.Denne CPLD bruges i indlejrede systemer, digital signalbehandling, kommunikationsenheder og industriel automatisering.

Vi leverer komponenter af høj kvalitet og tilpassede tjenester, så det er bedst at placere din bulkordre hos os for pålidelige CPLD-løsninger.

EPM7064STC100-7 Funktioner

• Logik med høj densitet: EPM7064STC100-7 er designet med 64 makroceller og 1.250 brugbare porte, hvilket gør det meget velegnet til implementering af komplekse logiske funktioner i digitale kredsløb.Denne arkitektur med høj densitet gør det muligt for at skabe komplicerede logiske design, samtidig med at effektiviteten opretholder effektiviteten i programmerbare logiske operationer.Den veloptimerede makrocellestruktur sikrer effektiv udnyttelse af tilgængelige ressourcer, der understøtter avancerede kombinations- og sekventielle logiske implementeringer.

• Hurtig ydelse: Bygget til højhastighedsbehandling fungerer EPM7064STC100-7 med en maksimal intern frekvens på 166,7 MHz, hvilket muliggør hurtig udførelse af logiske funktioner.Dens forplantningsforsinkelse på 7,5 ns sikrer minimal latenstid.Denne hurtige switching-kapacitet forbedrer enhedens evne til at håndtere højhastighedsdatabehandling, signalkonditionering og kontrolopgaver effektivt, hvilket gør det til et pålideligt valg for at kræve digitale systemer.

• Alsidig I/O: Med 68 programmerbare input/output-stifter giver EPM7064STC100-7 enestående fleksibilitet til integration i forskellige kredsløbsdesign.Understøtter både 3,3V- og 5V -logikniveauer giver det problemfri kompatibilitet med forskellige systemspændinger, hvilket eliminerer behovet for yderligere spændingsniveauskiftere.Denne tilpasningsevne gør den velegnet til applikationer i blandede spændingsmiljøer, hvilket sikrer bred anvendelighed på tværs af indlejrede systemer, industrielle kontroller og kommunikationsnetværk.

• In-system-programmerbarhed (ISP): En af fordelene ved EPM7064STC100-7 er dens 5,0V in-system-programmerbarhed (ISP), lettet gennem en IEEE STD.1149.1 JTAG -interface.Denne funktion gør det muligt at omprogrammere og ændre logiske funktioner uden at slappe af eller fysisk fjerne enheden, forenkle vedligeholdelse, fejlfinding og iterativ udvikling.ISP -kapaciteten reducerer nedetid og forbedrer fleksibiliteten i firmwareopdateringer, hvilket gør den uvurderlig til dynamisk og rekonfigurerbare digitale design.

EPM7064STC100-7 CAD-modeller

EPM7064STC100-7 Symbol

EPM7064STC100-7 fodaftryk

EPM7064STC100-7 3D-model

EPM7064STC100-7 Blokdiagram

De EPM7064STC100-7 Blokdiagram Viser, hvordan chipens logiske elementer er forbundet og kontrolleret.Det har fire logiske array -blokke (LABS), mærket A, B, C og D, der hver indeholder 16 makroceller.Disse makroceller udfører logiske funktioner, og de opretter forbindelse gennem et programmerbart Interconnect -array (PIA), som tillader fleksibel routing af signaler.Hvert laboratorium er knyttet til en I/O -kontrolblok, der håndterer op til 16 input/output -stifter pr. Lab.Diagrammet viser også globale kontrolsignaler (GCLK1, GCLK2, OE1 og GCLRN), der hjælper med at styre ur- og nulstillingsfunktioner til chippen.Nogle logiske porte behandler disse signaler, før de når forskellige dele af systemet.Designet af EPM7064STC100-7 gør det muligt at bruge det i forskellige programmerbare logiske applikationer, såsom tilstandsmaskiner, adresseafkodning og andre brugerdefinerede digitale kredsløb.Dens fleksible sammenkoblinger sikrer effektiv signalstrøm og pålidelig drift.

EPM7064STC100-7-specifikationer

|

Type |

Parameter |

|

Fabrikant |

Altera/Intel |

|

Serie |

Max® 7000s |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Programmerbar type |

I systemprogrammerbar |

|

Forsinkelsestid TPD (1) Max |

7,5 ns |

|

Spændingsforsyning - intern |

4,75V ~ 5,25V |

|

Antal logiske elementer/blokke |

4 |

|

Antal makroceller |

64 |

|

Antal porte |

1250 |

|

Antal I/O. |

68 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstype |

Overflademontering |

|

Pakke / sag |

100-tqfp |

|

Leverandørenhedspakke |

100-tqfp (14x14) |

|

Basisproduktnummer |

EPM7064 |

EPM7064STC100-7 In-system Programmering (ISP) sekvens

EPM7064STC100-7, en del af MAX 7000S CPLD-familien, følger en seks-trins programmering (ISP) -sekvens (ISP) for at sikre korrekt konfiguration.Denne proces giver dig mulighed for at programmere enheden uden at fjerne den fra kredsløbskortet.ISP -processen involverer skiftende instruktioner, adresser og data gennem TDI (testdata i) pin, mens du henter svar via TDO (testdata ud) pin.

Den første fase, Indtast ISP, sikrer, at I/O -stifter overgår glat fra brugertilstand til ISP -tilstand og kræver ca. 1ms.Dette efterfølges af Tjek ID, hvor enhedens silicium -ID læses for at bekræfte det korrekte mål.Derefter Bulk slet Trin skifter i sletning af instruktioner og anvender en 100 ms sletning af puls, hvilket rydder alle eksisterende data i EEPROM -cellerne.De Program Fasen følger, hvor adresser og data er sekventielt forskudt ind i enheden ved anvendelse af programmeringsimpulser til at konfigurere EEPROM -cellerne.Hver adresse skal programmeres individuelt, hvilket gør dette trin tidskrævende afhængigt af antallet af EEPROM-celler i enheden.

Når programmeringen er afsluttet, Verificere Scenen sikrer, at data er blevet gemt korrekt.Her anvendes læstimpulser på EEPROM -celler, og de hentede data sammenlignes med de forventede værdier.Hvis der findes uoverensstemmelser, kan omprogrammering være nødvendig.Endelig Afslut ISP Scenen sikrer, at I/O -stifter overgår tilbage til brugertilstand, hvilket kræver yderligere 1ms.Den samlede programmerings- eller verifikationstid påvirkes af to hovedfaktorer: pulstid, der kræves til EEPROM -sletning, programmering og læsningsoperationer og skiftende tid, som afhænger af TCK (testur) frekvens og antallet af cyklusser, der er nødvendige for at overføre instruktioner, adresser og data.Da forskellige ISP-kompatible enheder har varierende antal EEPROM-celler, er både samlede faste og variable tider unikke for hver enhed.Den samlede ISP -tid kan beregnes som en funktion af TCK -frekvens, antallet af målenheder og EEPROM -arkitekturen.

EPM7064STC100-7 Applications

Indlejrede systemer

EPM7064STC100-7 er vidt brugt i indlejrede systemapplikationer, hvor det fungerer som en fleksibel programmerbar logisk løsning til kontrol af forskellige perifere enheder, behandlingssignaler og implementering af brugerdefinerede protokoller.Dens evne til at interface med mikrokontrollere og sensorer gør det muligt at optimere systemets ydeevne, samtidig med at et kompakt fodaftryk opretholder et kompakt fodaftryk.Med sin højhastighedsdrift og lavt strømforbrug er det et fremragende valg til indlejrede applikationer, der kræver pålidelighed og effektivitet.

Digital Signal Processing (DSP)

I digital signalbehandling spiller EPM7064STC100-7 en rolle i implementeringen af filtre, signalmodulation og forskellige matematiske funktioner.Dens hurtige skifthastigheder og forsinkelse med lav forplantning gør det velegnet til håndtering af højfrekvente databehandlingsopgaver, hvilket sikrer minimal latenstid i signalomdannelse og manipulation.Det bruges ofte i lydbehandling, telekommunikation og radarsystemer.

Datakommunikation

EPM7064STC100-7 bruges i vid udstrækning i netværks- og datakommunikationssystemer på grund af dets evne til at håndtere logikintensive operationer som datarouting, buffering og fejlkorrektion.Dens programmerbare I/O -kapaciteter giver den mulighed for at tilpasse sig forskellige kommunikationsprotokoller, hvilket gør det til en værdifuld komponent i Ethernet -switches, routere og telekommunikationsinfrastruktur.Dens støtte til in-system-programmerbarhed (ISP) muliggør også feltopdateringer, hvilket forbedrer tilpasningsevnen i dynamiske netværksmiljøer.

Industriel automatisering

Industrielle applikationer kræver høj pålidelighed, holdbarhed og lavt strømforbrug, hvilket gør EPM7064STC100-7 til et foretrukket valg til programmerbare logiske controllere (PLC'er), motorstyringssystemer og automatiseret testudstyr.Med sin JTAG-baserede programmerbarhed i systemet giver det evnen til at forfine automatiseringsprocesser uden at kræve fysisk fjernelse eller redesign.Dens alsidighed i spændingskompatibilitet gør den også velegnet til grænseflade med en lang række sensorer og aktuatorer, der bruges i industrielle omgivelser.

EPM7064STC100-7 lignende dele

EPM7064STC100-7 Fordele

In-system programmerbarhed (ISP)

En af de største fordele ved EPM7064STC100-7 er dens evne til at blive omprogrammeret, mens den stadig er monteret i systemet.Dette eliminerer behovet for at fjerne chippen for opdateringer, reducere vedligeholdelsestid og forbedre effektiviteten.Du kan implementere designændringer uden at afbryde produktionen, hvilket gør det til en omkostningseffektiv løsning til langsigtede projekter.

Højhastighedsydelse

Enheden understøtter en høj intern driftsfrekvens på op til 166,7 MHz, hvilket giver mulighed for hurtige databehandling og responstider.Dette gør det ideelt til applikationer, der kræver signalbehandling, logisk kontrol og højhastighedsgrænseflade, hvilket sikrer glattere og mere pålidelig systemdrift.

Alsidig I/O -support

Med op til 68 konfigurerbare I/O-stifter og kompatibilitet med flere spændingsniveauer (3,3V, 5V og tolerante indstillinger for 2,5V, 3,3V og 5V) giver EPM7064STC100-7 fleksibilitet i systemdesign.Det tillader problemfri integration i forskellige kredsløb og understøtter blandede spændingsmiljøer, hvilket reducerer kompatibilitetsproblemer med andre komponenter.

Pålidelig drift på tværs af miljøer

EPM7064STC100-7 er designet til at fungere inden for et temperaturområde fra 0 ° C til 70 ° C og sikrer en konsekvent og stabil drift under forskellige forhold.Denne pålidelighed gør det til et foretrukket valg til applikationer, hvor miljømæssig stabilitet er påkrævet, såsom industriel automatisering, telekommunikation og indlejrede kontrolsystemer.

EPM7064STC100-7 Pakning Pin-Out Diagram

EPM7064STC100-7 er en CPLD (kompleks programmerbar logikenhed) fra Altera's MAX 7000S-serie, der ligger i en 100-polet tynd quad flad pakke (TQFP-100).Denne pakketype er designet til overflademonteringsapplikationer, der tilbyder en balance mellem høj pindensitet og kompakt størrelse.De Pin-out diagram Følger et nummereringsskema mod uret med pin 1 placeret i øverste venstre hjørne af pakken.Bevægende mod uret, de første 25 stifter optager venstre side, stifter 26 til 50 er placeret langs den nederste kant, stifter 51 til 75 fortsætter langs højre side, og stifterne 76 til 100 distribueres langs den øverste kant.De TQFP-100-pakke Har tynde ledninger, der strækker sig udad fra alle fire sider af den flade, firkantede krop.Dette design forbedrer overflademonteringskompatibilitet, mens den opretholder tilstrækkelig stiftafstand for let lodning og montering.Leadhøjden (afstand mellem tilstødende stifter) er typisk 0,5 mm, hvilket optimerer signalintegritet, mens det samlede fodaftryk minimerer det samlede fodaftryk.

EPM7064STC100-7 Producent

EPM7064STC100-7 er en CPLD (kompleks programmerbar logikenhed) oprindeligt udviklet af Altera, et halvlederfirma, der er kendt for sine programmerbare logiske løsninger.I 2015, Intel Erhvervet Altera, der integrerer sine FPGA- og CPLD -produktlinjer i Intels Programmerbare Solutions Group (PSG).Siden da er EPM7064STC100-7 blevet mærket under Intel, selvom den er blevet markeret som forældet.Intel opretholdt som producent den arvestøtte til MAX® 7000S -serien CPLDS, inklusive denne model, mens den gradvist flyttede sit fokus mod moderne FPGA og programmerbare logik -teknologier.

Konklusion

EPM7064STC100-7 samler komplekse funktioner, hurtig ydelse og lette opdateringer i en chip, hvilket beviser dens værdi i udfordrende digitale opsætninger.Denne guide har vist, hvordan den fungerer, hvad den bruges til, og hvordan den passer ind i forskellige elektroniske systemer.Det hjælper med at få enheder til at køre glat og effektivt, hvilket beviser, at det stadig er meget nyttigt til mange applikationer.Denne vejledning giver et klart overblik over, hvordan EPM7064STC100-7 kan hjælpe med at forbedre elektroniske design og systemoperationer effektivt.

Datablad PDF

EPM7064STC100-7 Datablad:

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Hvordan udbredte forplantningsforsinkelsen af EPM7064STC100-7-kredsløbets ydelse?

En 7,5NS-forplantningsforsinkelse sikrer signalbehandling med lav latens, hvilket gør denne CPLD egnet til højhastighedsapplikationer såsom digital signalbehandling (DSP), kommunikationssystemer og industriel automatisering, der kræver præcis timingkontrol.

2. kan EPM7064STC100-7 programmeres ved hjælp af moderne udviklingsværktøjer?

Ja, det kan programmeres ved hjælp af Intels Quartus II -software (tidligere Altera Quartus) sammen med en passende JTAG -programmør.Imidlertid kan støtte til ældre CPLD'er som EPM7064STC100-7 være begrænset i nyere kvartusversioner, så du kan muligvis bruge ældre versioner som Quartus II 13.0 SP1, som stadig understøtter MAX® 7000S-serien.

3. understøtter EPM7064STC100-7-malemiljøerne blandet spænding?

Ja, det understøtter både 3,3V og 5V logikniveauer, hvilket gør det kompatibelt med en lang række digitale kredsløb.Denne fleksibilitet er nyttig til grænseflade-arv 5V-komponenter med moderne 3,3V-systemer uden yderligere niveau-skiftende kredsløb.

4. Hvad er den bedste metode til fejlfinding af en EPM7064STC100-7-baseret design?

For at fejlfinde kan du bruge Quartus SignalTap II -logiske analysator eller eksterne oscilloskoper og logiske analysatorer til at overvåge signaler.Hvis fejlfinding af JTAG -programmeringsproblemer, skal du sikre dig, at TDI, TDO, TCK og TMS -forbindelser er korrekte, og at du bruger en kompatibel USB -blaster eller ByteBlasterMV -programmør.

5. Kan jeg programmere EPM7064STC100-7 uden at fjerne det fra mit kredsløbskort?

Ja.Den 5.0V in-system-programmerbarhed (ISP) via JTAG (IEEE 1149.1) giver dig mulighed for at omprogrammere enheden, mens den forbliver i systemet.Dette gør firmwareopdateringer, fejlsøgning og test meget mere effektiv sammenlignet med traditionelle CPLD'er.

Komplet guide til 10K -modstanden: farvekode, applikationer og kredsløbsanvendelser

på 2025-03-10

Kondensatorer vs. batterier: Hvilket er bedst til dine energibehov?

på 2025-03-07

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-19 147781

-

USB-C pinout og funktioner

på 2000-04-19 112052

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-19 111352

-

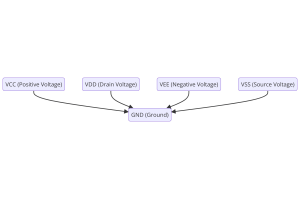

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-19 83807

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79613

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66992

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63117

-

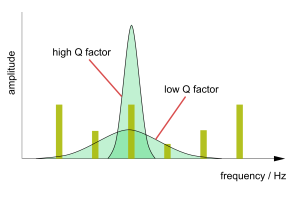

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63051

-

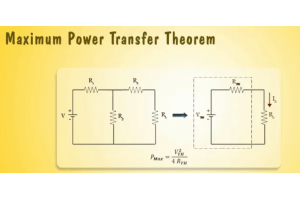

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52202