EPM7256AETC144-10N CPLD: Datablad, specifikationer, applikationer og programmeringsvejledning

EPM7256AETC144-10N er en programmerbar logikenhed (CPLD) fra Intels MAX® 7000A-serie.Denne chip er designet til hurtig ydelse, der kører op til 172,4 MHz med en 10 ns forsinkelse.Denne guide forklarer alt om denne CPLD, inklusive dens funktioner, specifikationer, anvendelser, hvordan man programmerer det og dets pin -layout.Hvis du har brug for en pålidelig, programmerbar chip til digitale kredsløb, hjælper denne artikel dig med at forstå, hvordan den fungerer.Katalog

EPM7256AETC144-10N Beskrivelse

De EPM7256AETC144-10N er en højtydende CPLD fra Intels MAX® 7000A-serie, der er skræddersyet til krævende logiske integrationsopgaver.Denne enhed kan prale af 256 makroceller og omkring 5.000 brugbare porte, hvilket letter betydelig designfleksibilitet og nytteværdi i komplekse digitale miljøer.Betjening med en maksimal frekvens på 172,4 MHz med en forplantningsforsinkelse på kun 5,5 ns, er den konstrueret til hurtig drift.EPM7256AETC144-10n, der er designet med en 3,3V driftsspænding og pakket i en kompakt 144-polet tynd quad-fladpakke (TQFP), understøtter kravene til robuste logiske design.Den EPM7256AETC144-10N anvender EEPROM-baserede ikke-flygtige konfigurationshukommelse, hvilket muliggør permanent opbevaring af programmeringsdata.Denne funktion kombineret med programmerbarhed i systemet via JTAG-interface giver lethed i opdateringer og feltprogrammering, forbedring af langvarig anvendelighed uden behov for fysisk rekonfiguration eller udskiftning.

Sikre dine projekter med pålidelig, feltprøvet teknologi ved at placere din bulkordre til EPM7256AETC144-10N med os i dag og sikre, at du har en solid CPLD-løsning.

EPM7256AETC144-10N CAD-modeller

EPM7256AETC144-10N Symbol

EPM7256AETC144-10N Fodaftryk

EPM7256AETC144-10N 3D-model

EPM7256AETC144-10N Funktioner

Makroceller:Denne enhed er udstyret med 256 makroceller.Makroceller er de konfigurerbare logiske komponenter, der giver CPLD mulighed for at udføre forskellige logiske funktioner.

Brugbare porte:Det giver cirka 5.000 brugbare porte.Dette henviser til den ækvivalente mængde af grundlæggende logiske porte (som og, eller, ikke), der kan konfigureres inden for enheden.

I/O -stifter:CPLD har 120 input/output -stifter, der giver mulighed for omfattende interface med andre dele af en brugers elektroniske design.

Formeringsforsinkelse (TPD):Den maksimale forsinkelse af formering er 10 nanosekunder, der bestemmer, hvor hurtigt CPLD kan behandle indgangssignaler og producere output.

Driftsfrekvens:Det kan fungere ved frekvenser op til 95,2 MHz, hvilket definerer den hastighed, hvormed enheden kan udføre logikoperationerne.

Forsyningsspænding:Enheden fungerer ved en forsyningsspænding på 3,3V, der tilpasser sig almindelige lavspændings digitale logikniveauer.

Pakke:Den findes i en 144-polet tynd quad flad pack (TQFP), en kompakt pakketype, der er gunstig til at minimere den krævede plads på trykte kredsløbskort.

Driftstemperaturområde:Driftstemperaturområdet er fra 0 ° C til 70 ° C, hvilket sikrer pålidelig ydelse over en lang række miljøforhold.

Programmbarhed i systemet:CPLD understøtter programmerbarhed i systemet via en IEEE STD.1149.1 Joint Test Action Group (JTAG) interface, hvilket muliggør programmering og omprogrammering af logikenheden inden for den endelige hardwarekonfiguration.

EPM7256AETC144-10N Block Diagram

De EPM7256AETC144-10N er en Kompleks programmerbar logikenhed (CPLD) med fire Logic Array Blocks (Labs) , hver indeholder 16 makroceller, i alt 64 makroceller.Disse makroceller håndterer både kombination og sekventiel logik, hvilket gør enheden fleksibel til forskellige digitale logiske applikationer.I midten af CPLD er Programmerbar Interconnect Array (PIA), der forbinder alle laboratorier, hvilket sikrer effektiv signalruting.Hvert laboratorium kommunikerer med PIA ved hjælp af 36 interconnect -linjer, hvilket gør det muligt at dele signaler og forarbejdes effektivt.Enheden har I/O -kontrolblokke på hver side, der understøtter 2 til 16 I/O -stifter pr. Lab.Disse blokke hjælper med at administrere input- og outputfunktioner, der forbinder CPLD til eksterne kredsløb.Kontrolsignaler som Global Clocks (GCLK1, GCLK2), Output Aktiverer (OE1) og Global Reset (GCLRN) hjælper med at synkronisere logiske operationer på tværs af enheden.Derudover administrerer logiske porte ur og nulstiller signaler, hvilket sikrer glat drift.Denne CPLD er designet til højhastighedslogikbehandling, der tilbyder programmerbarhed, effektiv signalruting og pålidelig I/O-kontrol, hvilket gør den velegnet til indlejrede systemer, kommunikation og industriel automatisering.

EPM7256AETC144-10N Specifikationer

|

Type |

Parameter |

|

Fabrikant |

Altera/Intel |

|

Serie |

MAX® 7000A |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Programmerbar type |

I systemprogrammerbar |

|

Forsinkelsestid TPD (1) Max |

10 ns |

|

Spændingsforsyning - intern |

3V ~ 3.6V |

|

Antal logiske elementer/blokke |

16 |

|

Antal makroceller |

256 |

|

Antal porte |

5000 |

|

Antal I/O. |

120 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstype |

Overflademontering |

|

Pakke / sag |

144-LQFP |

|

Leverandørenhedspakke |

144-tqfp (20x20) |

|

Basisproduktnummer |

EPM7256 |

EPM7256AETC144-10N applikationer

Kunstig intelligens

Denne CPLD anvendes i AI -hardwareacceleratorer til at håndtere komplekse beregninger, der kræves til behandling af AI -algoritmer effektivt, hvilket forbedrer både hastighed og pålidelighed i AI -applikationer.

5G -teknologi

I området 5G-kommunikation er EPM7256AETC144-10N bedst til signalbehandling og styring af kommunikationsprotokoller.Dens højhastighedslogiske operationer letter den hurtige behandling, der er nødvendig i den næste generation af trådløse systemer.

Cloud computing

Inden for datacentre forbedrer denne enhed behandlingsfunktioner, der tjener som komponent til styring af høje mængder data og komplekse beregninger, hvilket understøtter infrastrukturen for skytjenester.

Forbrugerelektronik

CPLD finder applikationer inden for forbrugerelektronik såsom fjernsyn og spilkonsoller, hvor det udfører brugerdefinerede logiske funktioner, der forbedrer enhedens funktionaliteter og oplevelse.

Trådløs teknologi

Det bruges i trådløse kommunikationsenheder til at modulere og demonstrere signaler, hvilket sikrer effektiv og effektiv kommunikation i enheder såsom routere og cellulære modemer.

Industriel kontrol

Denne enhed er integreret i automatiseringssystemer i industrielle omgivelser, hvor den kontrollerer maskiner og styrer processer, hvilket bidrager til øget produktivitet og sikkerhed.

Internet of Things (IoT)

I IoT-enheder administrerer EPM7256AETC144-10N databehandlings- og kommunikationsopgaver, fantastisk til den sømløse drift af tilsluttede enheder i smarte hjem og industrier.

Medicinsk udstyr

CPLD anvendes i medicinsk udstyr til opgaver såsom dataindsamling og signalbehandling, der spiller en rolle i pålideligheden og effektiviteten af medicinsk diagnostik og behandlingsudstyr.

EPM7256AETC144-10N lignende dele

EPM7256AETC144-10N fordele

Høj logikdensitet

Denne enhed pakker 256 makroceller og cirka 5.000 brugbare porte, hvilket muliggør implementering af komplekse logiske kredsløb inden for en enkelt chip.Denne høje logikdensitet letter mere integrerede og kompakte design, hvilket reducerer det overordnede komponenttælling og forenkler bestyrelseslayouts.

In-system programmerbarhed (ISP)

Med programmerbarhed i systemet via en IEEE STD.1149.1 JTAG-interface, EPM7256AETC144-10N giver mulighed for nem programmering og omprogrammering direkte inden for kredsløbet.Denne kapacitet er uvurderlig til hurtig prototype og iterative designprocesser, hvilket gør det muligt at foretage justeringer uden at skulle udskifte chippen.

Hurtig udbredelsesforsinkelse

Med en maksimal udbredelsesforsinkelse på kun 10 ns sikrer denne CPLD hurtig behandling af input og output til applikationer, der kræver højhastighedsdatahåndtering og rettidige svar, såsom videobehandling og højfrekvente handelssystemer.

Lavt strømforbrug

EPM7256AETC144-10N, der arbejder på en 3,3V-forsyningsspænding, er optimeret til energieffektivitet.Dette lave strømforbrug er fordelagtigt i bærbare og batteridrevne enheder, hvor strømstyring er god til at udvide operationel levetid.

Omfattende I/O -kapaciteter

Enheden er udstyret med 120 I/O -stifter, hvilket giver omfattende tilslutningsmuligheder.Dette giver mulighed for fleksibel grænseflade med en lang række perifere enheder og andre systemkomponenter, hvilket gør det meget tilpasningsdygtigt til komplekse multi-enhedsmiljøer.

Opbevaring af ikke-flygtig konfiguration

Takket være sin EEPROM-baserede hukommelse bevarer CPLD sine konfigurationsindstillinger, selv efter at strømmen er slukket, hvilket sikrer, at enhedens funktionalitet forbliver konsistent på tværs af strømcyklusser.Denne funktion er nødvendig for applikationer, der kræver pålidelig, langsigtet ydelse uden behov for hyppig rekonfiguration.

EPM7256AETC144-10N Programmeringstrin

Programmering af EPM7256AETC144-10N-enheden involverer en seks-trins in-system-programmering (ISP) -proces:

1. Indtast ISP: Dette trin sørger for, at input- og output -dele af enheden skifter fra normal brug til programmeringstilstand glat.Det tager ca. 1 millisekund.

2. Kontroller ID: Inden du starter programmering, kontrollerer enheden sit eget ID.Dette trin er meget hurtigt.

3. Bulk slet: Dette rydder alle tidligere data fra enheden.Det gør dette ved at modtage en kommando til at slette alt og derefter vente på 100 millisekunder for at sikre, at alt slettes.

4. Program: Det er her de nye data sættes i enheden.For hvert stykke data sendes det til den korrekte adresse på enheden, og derefter sørger en speciel puls for, at den er gemt korrekt.

5. Kontrol: Efter programmering kontrollerer enheden, om alle data er korrekt gemt ved at læse dem tilbage og sammenligne dem med, hvad den skal være.

6. Afslut ISP: Dette trin skifter enheden tilbage fra programmeringstilstand til normal brugstilstand.Det tager også ca. 1 millisekund.

Den samlede tid, der er nødvendig til programmering, afhænger af, hvor længe hver puls varer, og hvor hurtigt data kan flytte ind og ud af enheden, som er påvirket af hastigheden på programmeringsuret, og hvor meget data der er at behandle.Forskellige enheder kan tage forskellige mængder tid, fordi de har forskellige mængder hukommelse til programmet.

EPM7256AETC144-10N PAKKE PIN-OUT Diagram

Diagrammet viser EPM7256AETC144-10N-pakkekontoret og pin-nummerering.Denne chip kommer i en TQFP-144 (tynd quad flad pakke med 144 stifter), hvilket betyder, at det har fine pitch-kundeemner på alle fire sider.Placeringen af stiften 1 er markeret med en lille prik, og PIN -tal øger mod uret rundt om pakken.Nøglehenvisningstifter som pin 1, pin 37, pin 73 og pin 109 Hjælp med orientering under PCB -samling.Konturdimensionerne definerer chipens fysiske størrelse for at sikre korrekt PCB -montering.Pinout -arrangementet giver mulighed for effektiv signalrutning, hvilket gør det velegnet til komplekse logiske applikationer.EPM7256AE er en del af MAX 7000A CPLD-serien med 256 makroceller og programmerbarhed i systemet.-10N -suffikset angiver en 10 ns hastighedskvalitet og en blyfri pakke.

EPM7256AETC144-10N Producent

EPM7256AETC144-10N er en kompleks programmerbar logikenhed (CPLD), der oprindeligt blev udviklet af Altera Corporation, som senere blev erhvervet af Intel Corporation i 2015. Siden overtagelsen blev Intel den officielle producent af Altera's FPGA- og CPLD -produktlinjer, inklusive MAX® 7000A -serien, som denne enhed hører til.EPM7256AETC144-10N er designet til højtydende applikationer med lav effekt, der understøtter programmerbarhed i systemet (ISP) via JTAG (IEEE 1149.1).Selvom Intel arvet Alteras CPLD -teknologi, er denne enhed siden blevet afbrudt og er nu klassificeret som forældet, hvilket betyder, at Intel ikke længere producerer eller understøtter den i aktiv fremstilling.

Konklusion

EPM7256AETC144-10N er en kraftfuld og fleksibel CPLD, der bruges i AI, 5G, cloud computing, industrielle maskiner, IoT og medicinsk udstyr.Det behandler data hurtigt, bruger lidt strøm og giver mulighed for let omprogrammering uden at fjerne dem fra kredsløbet.Det er stadig nyttigt til ældre design, der har brug for programmerbar logik med stabil ydeevne.Uanset om du arbejder med denne CPLD eller leder efter lignende alternativer, kan det at forstå dets design, programmering og fordele hjælpe dig med at udnytte det bedst i det i højhastigheds digitale applikationer.

Datablad PDF

EPM7256AETC144-10N DATASHEETS:

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. hvor mange logiske elementer eller porte kan EPM7256AETC144-10N håndtag?

EPM7256AETC144-10N leverer 256 makroceller og cirka 5.000 brugbare porte, hvilket giver mulighed for moderat komplekse logiske implementeringer.

2. Hvordan programmerer jeg EPM7256AETC144-10N, og hvilke værktøjer har jeg brug for?

EPM7256AETC144-10N understøtter in-system-programmerbarhed (ISP) via JTAG (IEEE 1149.1) interface.Du har brug for en Altera USB-Blaster eller Intel Quartus Prime-software til at skrive konfigurationsdata til chippen.

3. Hvad er forskellene mellem EPM7256AETC144-10N og EPM7256AETC144-7?

Den primære forskel er hastighed.EPM7256AETC144-10N har en maksimal udbredelsesforsinkelse på 10 ns, mens EPM7256AETC144-7 har en hurtigere 7 ns forsinkelse til applikationer med højere hastighed.Begge enheder deler den samme pakke, I/O -tælling og makrocellestruktur.

4. kræver EPM7256AETC144-10N en ekstern oscillator?

Nej, selve CPLD kræver ikke en ekstern oscillator, men det understøtter eksterne urindgange.Hvis dit design har brug for præcis timing, kan et eksternt ursignal bruges til at drive sine logiske operationer.

5. Hvad gør EPM7256AETC144-10N forskellig fra andre CPLD'er i MAX 7000A-serien?

Denne CPLD skiller sig ud på grund af sin højhastighedsydelse (10 ns forplantningsforsinkelse), 256 makroceller og 5.000 brugbare porte, hvilket gør det ideelt til komplekse logiske design.Det understøtter også in-system-programmerbarhed (ISP) via JTAG, i modsætning til nogle ældre modeller.

MPC8245LZU300D -processor: datablad, funktioner, applikationer og specifikationer

på 2025-03-13

En simpel guide til L1154 -batterier til daglig brug

på 2025-03-13

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-18 147767

-

USB-C pinout og funktioner

på 2000-04-18 111994

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-18 111351

-

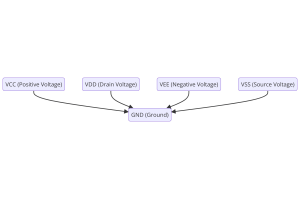

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-18 83758

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79555

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66952

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63098

-

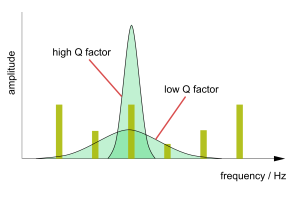

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63028

-

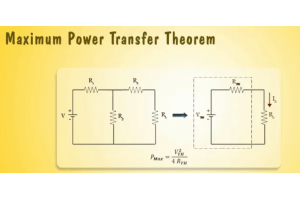

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54094

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52176