EPM7256SQC208-10 Guide: Funktioner, pinout, programmering, applikationer og datablad

Denne vejledning handler om EPM7256SQC208-10, en type programmerbar chip lavet af Intel (oprindeligt af Altera).Det kommer fra MAX® 7000S -familien og er kendt for at være hurtig, pålidelig og let at programmere, mens den allerede er inde i en enhed.Denne artikel forklarer, hvad chippen gør, hvordan den fungerer, hvor den bruges, og hvorfor det er et godt valg, hvis du har brug for en stærk og fleksibel logisk enhed til dit projekt.Katalog

EPM7256SQC208-10 Oversigt

De EPM7256SQC208-10 er en del af Intels (tidligere Altera) MAX® 7000S-familie, et højtydende CPLD-interval, der er kendt for sin robuste programmerbarhed og logiske optimeringsfunktioner.Denne model kan prale af omkring 5.000 brugbare porte og inkluderer 256 makroceller, der ligger inden for en 208-polet plast quad flad pack (PQFP).Det fungerer med en frekvens op til 128,2 MHz og understøtter en 5,0 V driftsspænding med en maksimal udbredelsesforsinkelse på 7,5 ns og et operationelt temperaturloft på +70 ° C.En nøglefunktion er dens programmerbarhed i systemet gennem en indbygget IEEE STD.1149.1 JTAG -interface, der muliggør dynamisk konfiguration.MAX® 7000S-enheder er fremstillet ved hjælp af avanceret CMOS-teknologi og tilbyder funktioner såsom pin-to-pin-logikforsinkelser så hurtige som 5 ns og tællerfrekvenser, der når op til 175,4 MHz.Familien præsenterer en række pakkeindstillinger og er designet med programmerbar makrocell-flip-flops, der bidrager til betydelige strømbesparelser over 50% reduktion i nogle tilfælde.Derudover inkluderer det en sikkerhedsbit til beskyttelse af proprietære design.

Hvis din organisation har brug for en solid programmerbar logisk løsning, er EPM7256SQC208-10 et pålideligt valg, så kontakt os i dag for at sikre din bulkordre.

EPM7256SQC208-10 CAD-modeller

EPM7256SQC208-10 Symbol

EPM7256SQC208-10 fodaftryk

EPM7256SQC208-10 3D-model

EPM7256SQC208-10 Funktioner

• Høj logikdensitet: EPM7256SQC208-10 giver ca. 5.000 brugbare porte og indeholder 256 makroceller.Denne høje logiske kapacitet gør den ideel til implementering af komplekse kombinationskredsløb og effektiv logisk integration i kompakte design.

• Hurtig præstation: Med en maksimal driftsfrekvens på 128,2 MHz og en forplantningsforsinkelse på kun 7,5 ns, sikrer denne CPLD hurtige behandlings- og hurtige responstider, der er gode til højhastighedsapplikationer.

• In-system programmerbarhed (ISP): Udstyret med en IEEE STD.1149.1 JTAG-interface, enheden giver mulighed for programmering og test i systemet uden behov for fysisk fjernelse, hvilket letter iterativ udvikling og opdateringer.

• Avanceret arkitektur: Ved hjælp af Alteras anden generation af MAX-arkitektur og fremstillet med avanceret CMOS-teknologi giver EPM7256SQC208-10 forbedret ydelse og holdbarhed, hvilket sikrer pålidelighed i forskellige operationelle miljøer.

• Power Management: Enheden har programmerbare strømbesparende tilstande, der kan reducere strømforbruget med over 50% pr. Makrocell, der understøtter energieffektive design og forlænger batteriets levetid i bærbare applikationer.

• Sikkerhedsfunktioner: En programmerbar sikkerhedsbit giver beskyttelse mod uautoriseret adgang og kopiering af proprietære design, der beskytter intellektuel ejendom effektivt.

• Brede driftsbetingelser: Betjening ved 5,0 V og i stand til at fungere i temperaturer op til +70 ° C, tilpasser dette CPLD sig til forskellige miljøforhold, hvilket gør det velegnet til både industrielle og kommercielle anvendelser.

• Fleksible I/O -standarder : Understøtter Multivolt ™ I/O -interface -operationer, kompatible med både 3,3 V og 5,0 V -systemer.Denne fleksibilitet tillader problemfri integration med eksisterende og ny hardware, hvilket reducerer systemkompleksiteten og omkostningerne.

• Designstøtte: EPM7256SQC208-10 understøttes af en række designværktøjer og programmeringshardwareindstillinger, forenkler udviklingsprocessen og tillader at fokusere på innovation snarere end kompatibilitetsproblemer.

EPM7256SQC208-10 Pinout-diagram

Dette diagram viser PIN-layoutet for EPM7256SQC208-10-chip fra Altera.Chippen har 208 stifter, arrangeret på alle fire sider i en firkantet form.Pin 1 starter i øverste venstre hjørne, og tallene går rundt om chippen i en retning mod uret, ned ad venstre side til pin 53, over bunden til pin 105, op ad højre side til pin 157 og tilbage til øverste højre.Etiketterne hjælper dig med at vide, hvor du skal starte, og hvordan du placerer chippen korrekt på et kredsløbskort.Navnet i midten, "EPM7256E / EPM7256S," betyder, at dette layout fungerer til begge chipversioner.Dette diagram er vigtigt, når man forbinder effekt, signaler eller programmeringslinjer til chippen.

EPM7256SQC208-10 Blokdiagram

Blokdiagrammet for EPM7256SQC208-10 viser, hvordan chippen er organiseret til at håndtere digitale logiske opgaver.Det har fire hovedlogikblokke kaldet Lab A, B, C og D. Hver blok indeholder 16 makroceller, som er de grundlæggende bygningsdele, der udfører logikarbejdet.Så i alt er der 64 makroceller inde i chippen.Omkring disse logiske blokke er I/O -kontrolblokke, der forbinder chippen til omverdenen gennem input- og udgangsstifter.Hver kontrolblok administrerer 6 til 16 stifter og lader signaler gå ind eller ud af chippen efter behov.

I midten er det programmerbare Interconnect Array (PIA), der fungerer som et motorvejssystem, der lader signaler bevæge sig mellem logiske blokke og I/O -stifter.Dette giver dig mulighed for at rute data, som du har brug for til dit design.Øverst til venstre viser diagrammet nogle kontrolindgange som Global Clock (GCLK), Output Enable (OE) og CLEAR (GCLR).Disse signaler hjælper med at styre timingen og opførslen af logikkredsløbene på tværs af chippen.

EPM7256SQC208-10-specifikationer

|

Type |

Parameter |

|

Fabrikant |

Altera/Intel |

|

Serie |

Max® 7000s |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Programmerbar type |

I systemprogrammerbar |

|

Forsinkelsestid TPD (1) Max |

10 ns |

|

Spændingsforsyning - intern |

4,75V ~ 5,25V |

|

Antal logiske elementer/blokke |

16 |

|

Antal makroceller |

256 |

|

Antal porte |

5000 |

|

Antal I/O. |

164 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstype |

Overflademontering |

|

Pakke / sag |

208-BFQFP |

|

Leverandørenhedspakke |

208-PQFP (28x28) |

|

Basisproduktnummer |

EPM7256 |

EPM7256SQC208-10 applikationer

Industriel automatisering

EPM7256SQC208-10 bruges i vid udstrækning i industrielle automatiseringssystemer.Dens høje logikdensitet og hurtige ydeevne muliggør komplekse kontrolopgaver, der grænser problemfrit med sensorer og aktuatorer.Denne CPLD er ideel til forbedring af præcision og effektivitet i produktionslinjer, processtyringssystemer og robotapplikationer.

Telekommunikation

I telekommunikation udmærker denne CPLD sig i styring af dataflow og signalintegritet på tværs af netværk.Det understøtter funktioner som signalkonvertering, routing og behandling i switches og routere, hvilket sikrer robuste og effektive kommunikationsinfrastrukturer.

Bilsystemer

I bilindustrien bidrager denne enhed til pålidelighed og sofistikering af systemer såsom motorstyringsenheder, infotainment-systemer og driverassistentteknologier.Dens robuste ydelse under forskellige forhold gør den velegnet til sikkerhedskritiske anvendelser.

Medicinsk udstyr

Precision og programmerbarhed af EPM7256SQC208-10 gør det værdifuldt i medicinsk udstyr, hvor nøjagtig kontrol og pålidelig drift er vigtig.Det bruges i enheder til overvågning af patientvitaler, styring af diagnostiske instrumenter og automatisering af behandlingslevering.

Rumfart og forsvar

I rumfart og forsvar anvendes EPM7256SQC208-10 i systemer, der kræver høje niveauer af pålidelighed og ydeevne, såsom satellitkommunikation, navigationshjælpemidler og militære hardwarekontrol.Dets evne til at operere under ekstreme forhold er gavnlig.

Uddannelses- og forskningsinstitutioner

Denne CPLD er også populær i uddannelsesmæssige omgivelser og forskningsprojekter, hvor dens omprogrammabilitet og fleksibilitet letter eksperimentering og læring i digital design og elektronik.Det giver mulighed for at prototype og teste forskellige logiske design effektivt.

EPM7256SQC208-10 lignende dele

EPM7256SQC208-10 programmeringstrin

1. Indtast ISP -tilstand

Dette indledende trin er vigtigt, da den overgår CPLD fra normal driftstilstand til in-system-programmering (ISP) -tilstand.Dette opnås ved at sende en bestemt kommando gennem JTAG -interface.Under denne proces er alle I/O-stifter af CPLD tri-state (deaktiveret) for at undgå interferens eller konflikter med andre kredsløbskomponenter.Overgangen til ISP -tilstand forbereder enheden til sikker programmering og tager ca. 1 millisekund.

2. Kontroller ID

En gang i ISP -tilstand udfører systemet en ID -kontrol for at sikre, at den korrekte enhed programmeres.Dette involverer at læse enhedens unikke silicium -ID gennem JTAG -interface.Dette trin er godt til at verificere, at programmeringskommandoer og data vil blive sendt til den rigtige enhed, hvilket forhindrer fejlagtig programmering og potentiel enhedsskade.

3. Bulk slet

Inden nye data kan programmeres, skal de eksisterende data inden for CPLD slettes.Bulk -sletningstrinnet rydder effektivt alle de programmerbare celler inden for enheden.Dette gøres ved at skifte i sletningsinstruktionen og derefter anvende en 100 millisekund puls, der sletter hele chippen.Dette trin er vigtigt for at sikre, at ingen rester af tidligere konfigurationer forstyrrer den nye programmering.

4. Program

Dette trin involverer den faktiske programmering af CPLD, hvor de nye konfigurationsdata er skrevet til enheden.Data og tilsvarende adresser forskydes til enheden gennem JTAG -interface.Hvert adresse og datapar kræver en programmeringspuls for at sikre, at dataene er korrekt skrevet ind i CPLD's ikke-flygtige hukommelsesceller.Dette trin gentages for hvert datapunkt på tværs af enhedens hukommelseskort.

5. Kontroller

Efter programmering er det nødvendigt at verificere, at dataene er blevet skrevet korrekt til enheden.Dette verifikationstrin involverer at læse de programmerede data tilbage fra hver adresse og sammenligne dem med de originale inputdata.Dette trin sikrer dataintegritet og bekræfter, at programmeringsprocessen har været en succes uden fejl.

6. Afslut ISP -tilstand

Det sidste trin i programmeringsprocessen er at forlade ISP -tilstand og returnere CPLD til normal operationel tilstand.Dette gøres ved at sende en anden kommando via JTAG -interface.Efter vellykket udgang genaktiveres I/O -stifterne, og enheden genoptager normal funktion.Dette trin tager også typisk ca. 1 millisekund.

EPM7256SQC208-10 Fordele

Ikke-flygtig konfiguration

EPM7256SQC208-10 bruger EEPROM-teknologi, så den kan gemme sin konfiguration permanent.Denne ikke-flygtige karakter betyder, at enheden ikke behøver at genindlæse sine konfigurationsdata fra ekstern hukommelse, hver gang den er tændt.Dette resulterer i hurtigere opstartstider og reducerer den samlede kompleksitet af hardware -designet ved at eliminere behovet for yderligere konfigurationslagringskomponenter.

In-system programmerbarhed (ISP)

Et af de fremtrædende funktioner i EPM7256SQC208-10 er dens støtte til programmerbarhed i systemet.Dette gør det muligt at programmeres og omprogrammeres, mens den er indlejret i slutapplikationen uden at skulle fjernes fysisk.Denne kapacitet forenkler opdateringer og ændringer, hvilket giver fleksibilitet og brugervenlighed under udvikling og gennem hele produktets livscyklus.

Høj I/O -tælling og logikdensitet

Enheden tilbyder en betydelig mængde logiske ressourcer og I/O -stifter med 256 makroceller og 164 bruger I/O -stifter.Denne høje I/O -tælling og logikdensitet muliggør integration af flere funktioner i en enkelt chip, hvilket letter mere komplekse design, mens den bevarer plads på PCB.Denne fordel er gavnlig i applikationer, hvor bestyrelsesrummet er på en premium, og multifunktionalitet er vigtig.

Hurtig pin-to-pin forsinkelse

Med en maksimal pin-to-pin-forsinkelse på kun 10 ns kan EPM7256SQC208-10 udføre højhastighedslogikoperationer.Denne hurtige responstid er stor i applikationer, der kræver hurtige behandlingsfunktioner, såsom højhastighedskommunikation eller computing, hvilket sikrer, at systemet opfylder strenge ydelseskriterier.

Bred spændingskompatibilitet

EPM7256SQC208-10 er designet til at være fleksibel med hensyn til spændingskompatibilitet, hvilket understøtter intern drift ved 5 V og I/O-niveauer ved 3,3 V. Denne dobbeltspændingsevne giver enheden mulighed for let at interface med både 3,3 V og 5 V-systemer, hvilket reducerer behovet for spændingsniveauoversættelser og forenkler systemdesign.

EPM7256SQC208-10 Emballagedimensioner

• Pakningstype: 208-BFQFP (Plastic Quad Flat Package)

• Antal stifter: 208 fører

• Kropsstørrelse (L × W): 28 mm × 28 mm

• Monteringstil: Surface Mount Technology (SMT)

• Bly tonehøjde: Typisk 0,5 mm mellem stifter (standard for BFQFP)

• Pakningsmateriale: Plast

• Pakketykkelse: Ca. 3,5 mm (varierer lidt af producenten)

• Termiske egenskaber: Ingen udsat pude;Standard omgivelsesafledning via bestyrelse

• Bakke emballage: Leveres i bakker til volumenhåndtering og pick-and-place Automation

EPM7256SQC208-10 Producent

EPM7256SQC208-10 blev oprindeligt udviklet og fremstillet af Altera Corporation, en førende pioner inden for programmerbare logiske enheder, der er kendt for sin MAX® 7000S -serie af CPLDS.I 2015 blev Altera erhvervet af Intel Corporation, en af verdens største halvlederproducenter.Siden overtagelsen har Intel fortsat med at støtte og integrere Altera's CPLD- og FPGA -teknologier under sin programmerbare løsningsgruppe.EPM7256SQC208-10 repræsenterer Intels arv i at tilbyde højtydende, programmerbare logiske løsninger i systemet, der er skræddersyet til en lang række industrielle, telekommunikation og indlejrede applikationer.Skønt nu klassificeret som forældet, afspejler delen Intels mangeårige engagement i pålidelige og fleksible programmerbare logiske enheder.

Konklusion

EPM7256SQC208-10 er en smart og pålidelig chip, der hjælper med at få digitale systemer til at køre glat.Det sparer strøm, understøtter forskellige spændinger og giver dig mulighed for at programmere det, mens den allerede er installeret, hvilket gør opdateringer let.Selvom det nu er en ældre chip, bruger andre den stadig, fordi det fungerer godt i alle slags systemer.Hvis du har brug for en solid chip til at kontrollere logik i dit design, er denne en fantastisk mulighed.Kontakt os i dag, hvis du vil bestille det i bulk.

Datablad PDF

EPM7256SQC208-10 Datablad:

Cylindriske batteriholdere.pdf

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Hvilke programmeringsværktøjer er kompatible med EPM7256SQC208-10?

Du kan bruge Intels Quartus II-software (tidligere Altera Quartus) sammen med en JTAG-kompatibel programmør som USB-Blaster, til at konfigurere og programmere EPM7256SQC208-10 direkte i systemet.

2. kan jeg omprogrammere EPM7256SQC208-10 flere gange?

Ja, EPM7256SQC208-10 understøtter flere omprogrammeringscyklusser ved hjælp af dens EEPROM-baserede in-system-programmerbarhed, hvilket gør det ideelt til iterativ designudvikling eller opdateringer efter installation.

3. kan EPM7256SQC208-10 håndtere barske driftsbetingelser?

Det fungerer pålideligt inden for et kommercielt temperaturområde fra 0 ° C til +70 ° C, hvilket er tilstrækkeligt til de fleste industrielle og indlejrede applikationer, dog ikke for ekstreme miljøer eller bilkvalitet.

4. kan jeg stadig programmere EPM7256SQC208-10 uden at fjerne det fra kredsløbskortet?

Ja.Chip understøtter in-system-programmerbarhed (ISP) via JTAG, så du kan omprogrammere den, mens den allerede er loddet på dit bord, hvilket sparer tid og kræfter under udvikling eller vedligeholdelse.

5. Hvad gør EPM7256SQC208-10 bedre end en standard mikrokontroller til logiske opgaver?

I modsætning til mikrokontrollere er EPM7256SQC208-10 en CPLD, der udmærker sig ved at udføre parallelle logiske operationer med præcis timing.Det er ideelt, når du har brug for hurtig, deterministisk digital kontrol over flere signaler.

Demorgan's sætninger forklarede: forenkling af logiske udtryk for bedre kredsløbsdesign

på 2025-04-25

Norton teorem grundlæggende og kredsløbseksempler

på 2025-04-24

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-18 147764

-

USB-C pinout og funktioner

på 2000-04-18 111987

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-18 111351

-

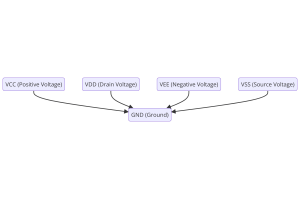

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-18 83751

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79542

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66949

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63091

-

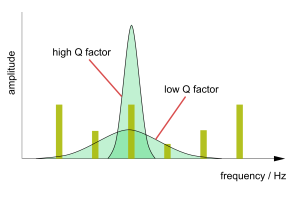

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63028

-

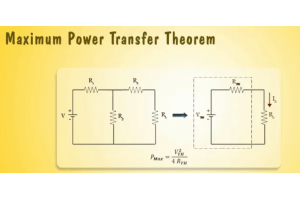

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54092

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52172