Forbedring af FPGA -design med brugerbegrænsningsfiler (UCF) til Xilinx ISE -værktøjer

Denne guide undersøger rollen som brugerbegrænsningsfiler (UCFS) i forbedring af FPGA -design med Xilinx ISE -værktøjer.UCF'er tillader at tilføje specifikke begrænsninger for bedre at kontrollere timing, logik og placering, hvilket øger designnøjagtigheden, ydeevnen og pålideligheden.Ved at vise, hvordan man anvender disse begrænsninger effektivt, hjælper guiden med at forenkle designprocessen, skære ned debugging -tid og sikre en vellykket projektlevering.Katalog

Formål og rolle af UCFS i FPGA -design

I FPGA -design spiller brugerbegrænsningsfiler (UCFS) en rolle i at kontrollere, hvordan logikken syntetiseret fra din kode bliver fysisk implementeret på chippen.Disse filer lader specificere vigtige parametre, såsom timingbegrænsninger, pinopgaver og detaljer om arealplacering, der direkte kan påvirke, om et design opfylder ydelseskrav eller ej.Tænk på UCF'er som tegninger, der sikrer, at alt er placeret korrekt, fungerer efter planen og passer pænt på plads.Processen med begrænsningsindstilling begynder i de tidlige udviklingsstadier.Start med at oprette en UCF -fil før syntese, og sikre, at parametre er låst lige fra starten.Efter syntese genereres yderligere begrænsningsfiler som Netlist -begrænsningsfilen (NCF) og fysisk begrænsningsfil (PCF) for at afspejle ændringer, der er foretaget i logikken og for at afslutte fysiske begrænsninger.Hver af disse filer bygger på det foregående trin og raffinerer gradvist designet.UCFS er tekstbaserede filer skrevet i ASCII-format, hvilket betyder, at de kan redigeres ved hjælp af grundlæggende tekstredaktører eller mere specialiserede værktøjer som Xilinx-begrænsningsredaktøren.Denne enkelhed gør UCFS meget tilgængelig og fleksibel til at dykke ned i detaljerne i begrænsningsindstillinger uden at have brug for alt for komplekse værktøjer.

Hvor begrænsninger former FPGA -design?

I FPGA -design spiller begrænsninger en rolle i udformningen af, hvordan chippen fungerer og interagerer med eksterne enheder.Disse begrænsninger er defineret i en UCF (brugerbegrænsningsfil), der fungerer som et detaljeret instruktionssæt til designværktøjet, der specificerer, hvordan FPGAs interne komponenter skal tilsluttes og styres.De vigtigste begrænsninger inkluderer timingbegrænsninger, der sikrer signaler, der rejser mellem komponenter inden for en bestemt tidsramme for at opretholde pålidelig ydelse i den ønskede urhastighed.Pinopgaver kortlægger fysiske FPGA -stifter til eksterne enheder såsom sensorer, hukommelsesmoduler eller kommunikationsgrænseflader, hvilket sikrer nøjagtige forbindelser.Område -begrænsninger kontrollerer placeringen af logiske blokke på chippen for at undgå overbelastning, reducere forsinkelser og optimere ressourceforbruget.Uden disse begrænsninger ville automatiserede værktøjer træffe placering og routingbeslutninger, men ofte med suboptimale resultater, hvilket fører til timingproblemer, flaskehalse eller ineffektive chip -layouts.Ved at bruge UCF -filer bevarer mange kontrol over disse kritiske aspekter, hvilket resulterer i bedre ydelse, effektivitet og pålidelighed i FPGA -design.

Den iterative karakter af begrænsningsforfining

FPGA-design er sjældent en en-og-gjort-proces.Begrænsninger justeres gentagne gange i hele udviklingscyklussen, når designet udvikler sig, og nye udfordringer opstår.Andre finjusterer UCF -filer for at opfylde præstationsmål, løse timingproblemer eller tilpasse sig ændrede projektkrav.Denne iterative forfining er en vigtig del af FPGA -arbejdsgangen.For eksempel, hvis du bemærker, at en signalsti tager for lang tid at udbrede mellem to komponenter, kan de muligvis ændre UCF for at ændre timingbegrænsningen eller flytte disse komponenter for at reducere forsinkelser.Tilsvarende, hvis en PIN -tildeling er i konflikt med ekstern hardware, kan UCF redigeres for at løse misforholdet.Hver revision af UCF bevæger designet tættere på det ønskede resultat, hvor enhver justering underviser mere om de afvejninger, der er involveret i FPGA-optimering.Denne cyklus med test, justering og læring forbedrer ikke kun designet, men skærper også færdigheder.

Fordele ved at bruge UCF'er

Anvendelse af begrænsninger gennem UCF -filer giver flere praktiske fordele, der bidrager til succes med FPGA -projekter:

• Forbedret timingnøjagtighed: Veludviklede timingbegrænsninger sikrer, at FPGA fungerer pålideligt med den ønskede urhastighed, hvilket undgår fejl forårsaget af signalforsinkelser.

• Bedre ressourceudnyttelse: Områdebegrænsninger forhindrer, at logiske blokke placeres for tæt sammen eller for langt fra hinanden, optimerer chiprummet og forbedrer ydeevnen.

• Forenklet debugging: Ved at kontrollere pinopgaver og signalruting hjælper UCFS med at reducere routingkonflikter, hvilket gør det lettere at diagnosticere og løse problemer under test.

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Applikationsspecifikke standardprodukter (ASSPS): Kørsel af innovation inden for moderne elektronik

på 2025-01-08

System på en programmerbar chip (SOPC): teknologi, design og applikationer

på 2025-01-08

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-18 147760

-

USB-C pinout og funktioner

på 2000-04-18 111974

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-18 111351

-

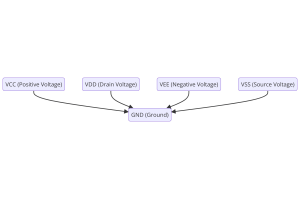

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-18 83742

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79527

-

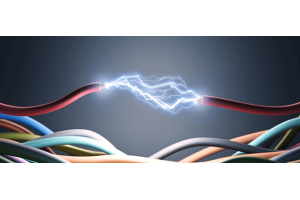

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66939

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63086

-

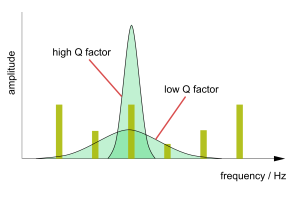

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63025

-

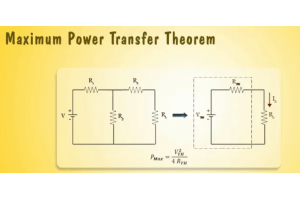

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54092

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52167