HDL: Låsning af innovation inden for digital kredsløbsdesign

Denne guide udforsker hardwarebeskrivelsessprog (HDL'er), vigtige værktøjer til at omdanne abstrakte design til ægte, fremstillede kredsløb.Vi dækker deres udvikling, applikationer i ASIC og FPGA -design og deres indflydelse på moderne elektronik.Gennem eksempler og ekspertindsigt sigter denne vejledning på at uddybe din forståelse af HDL'er og styrke både din teori og praktiske færdigheder.Oplev, hvordan HDLS bro mellem ideen mellem ideer og fysiske enheder, hvilket driver innovation inden for teknologi.Katalog

HDL's rolle i digital design

Hardware Beskrivelse Sprog (HDL) spiller en rolle i designet af digitale systemer ved at tilvejebringe en struktureret måde at modellere komplekse kredsløb på.Det gør det muligt at opdele store systemer i mindre, håndterbare moduler, der testes og verificeres ved hjælp af elektroniske designautomations -værktøjer.Når de er valideret, syntetiseres disse moduler til netlister på gate-niveau og omdannes til fysiske kredsløb gennem ASIC- eller FPGA-placering og routing.HDL driver innovation, der er vidt brugt i brancher som Silicon Valley, innovation ved at hjælpe med at balancere designbegrænsninger med kreative løsninger, hvilket gør det til en nøglekomponent i at fremme digital teknologi.

Historisk udvikling af HDL

Udviklingen af hardwarebeskrivelsessprog (HDL'er) spænder over årtier, der udvikler sig fra fragmenterede, nicheværktøjer til standardiserede, brancheomfattende løsninger som VHDL og Verilog i slutningen af 1980'erne.Disse standardiserede HDL'er samlede designpraksis og forbedret samarbejde.Efterhånden som teknologien avancerede udvidede HDLS til at understøtte mere komplekse systemer, bygge bro over hardware og softwaredesign med nye sprog som SystemC og Superlog.HDLS har vist deres værdi i forbedring af kommunikation, reduktion af fejl og strømlining af designprocessen.Den igangværende udvikling af HDL'er afspejler behovet for kontinuerlig innovation for at imødekomme de skiftende krav til digital design til moderne teknologiudvikling.

Formål

Da integrerede kredsløb er blevet mere komplekse, drevet af Moore's lov siden 1970'erne, er designmetodologier skiftet fra at fokusere på individuelle komponenter til styring af systemniveau-dataflow og -timing.Dette skift førte til vedtagelse af Abstraktion af registeroverførselsniveau (RTL), som gør det muligt at koncentrere sig om logiske funktioner og timing uden at skulle adressere fremstillingsdetaljer tidligt.RTL -abstraktion, understøttet af hardwarebeskrivelsessprog (HDL'er), strømline designprocessen ved at afbalancere ydeevne, strøm og skalerbarhed.Det reducerer designcyklusser, forbedrer samarbejdet og hjælper med at forudse potentielle problemer, hvilket forhindrer dyre revisioner.Ved at fokusere på højere abstraktionsniveauer låser du større effektivitet, tilpasningsevne og innovation i det hurtigt udviklende tech -landskab.

Strukturelle egenskaber

Hardware Beskrivelse Sprog (HDLS) fungerer som tekstrammer, der definerer struktur, opførsel og timing af kredsløbssystemer.De fungerer som parallelle programmeringssprog, men er specifikt rettet mod styring af timing og hardwareforbindelser.HDLS fungerer på tværs af forskellige abstraktionsniveauer, strukturelle, adfærdsmæssige og registeroverførsel, for at nærme sig kredsløbsdesign fra forskellige perspektiver.På strukturelt niveau detaljerede HDLS -detaljerede komponenter og forbindelser, der ligner skemaer.Adfærdsniveauet fokuserer på, hvad kredsløbet skal gøre, mens registeroverførselsniveauet (RTL) beskriver dataflow og -operationer mellem registre, afbalancering af funktionalitet og hardware-specifikationer.HDL'er understøtter også logisk syntese, konvertering af design på højt niveau til kredsløb på gate-niveau og simulering, der tester funktionalitet før hardwareinstallation.I modsætning til traditionelle programmeringssprog modellerer HDL'er primært værktøjer, der fanger hardwareadfærd, hvilket gør dem vigtige for nøjagtigt, innovativt kredsløbsdesign.

Undersøgelse af dataflow i HDL

I modsætning til traditionelle programmeringssprog, der prioriterer kontrolstrøm, fokuserer HDLS på modellering af dataflow og timing i kredsløb til hardwareudvikling og simulering.Denne unikke evne til at fange den tidsmæssige opførsel af hardware adskiller HDLS bortset fra sprog som C ++.Moderne HDL'er, såsom SystemVerilog, blandes i stigende grad programmeringsparadigmer, der inkorporerer objektorienterede koncepter for at forbedre modulariteten og vedligeholdeligheden i komplekse systemdesign.HDL'er spiller også en rolle i logisk syntese, der omdanner beskrivelser på højt niveau til implementeringer på gate-niveau, hvilket sikrer, at abstrakte design er i overensstemmelse med fysiske begrænsninger.Derudover anvendes ikke-syntiserbare HDL-elementer til simulering og verifikation for nøje testkredsløbsadfærd inden produktionen.Når HDL'er fortsætter med at udvikle sig, vil de sandsynligvis vedtage mere software-lignende funktioner til at tackle voksende hardwarekompleksiteter og bygge bro mellem afstanden mellem hardware-præcision og venlig abstraktion.

Forbedring af integreret kredsløbsdesign med HDL

Hardware Beskrivelse Sprog (HDLS) strømline den komplekse proces med at designe integrerede kredsløb ved at omdanne abstrakte ideer til praktiske, eksekverbare planer.Mange bruger ofte flowdiagrammer og statsdiagrammer til at kortlægge kredsløbslogik, før de konverterer det til præcis HDL -kode, ligesom at skabe tegninger til konstruktion.Mens de overholder kredsløbskrav, bringer andre deres unikke stil til kodning ved at inkorporere algoritmer og scripting for at forenkle gentagne opgaver.Fejlkontrolværktøjer identificerer derefter problemer tidligt, hvilket sikrer pålidelighed inden syntese.Efter syntese er Netlists forberedt på fremstilling, hvad enten det er for FPGA'er eller ASIC'er, der fokuserer på enhedsspecifikationer for at undgå produktionsudfordringer.HDLS skaber en balance mellem kreativitet og præcision, hvilket muliggør innovative, men pålidelige kredsløbsdesign, der effektivt skrider frem fra koncept til fysisk realisering.

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Vitis Unified Software Platform: Accelerating Embedded Systems and Adaptive Computing med Xilinx

på 2025-01-07

Udviklingen og strategiske fremskridt inden for VLSI -teknologi

på 2025-01-06

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-19 147782

-

USB-C pinout og funktioner

på 2000-04-19 112062

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-19 111352

-

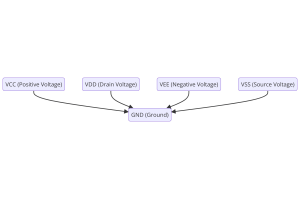

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-19 83818

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79635

-

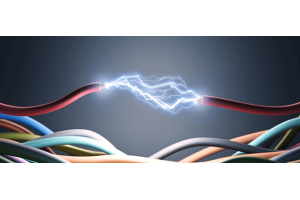

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66999

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63124

-

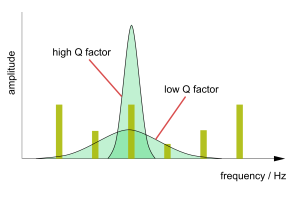

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63060

-

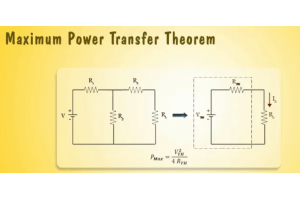

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52211