LFEC3E-3Q208C FPGA Oversigt: Funktioner, applikationer, programmering og specifikationer

I denne artikel lærer du om LFEC3E-3Q208C, en FPGA fra Lattice Semiconductor.Du kan se, hvad det er, de vigtigste funktioner, det tilbyder, og hvorfor det er nyttigt til mange mellemklasse-design.Indholdet leder dig også gennem dens specifikationer, applikationer og trin-for-trin-programmeringsproces sammen med dens fordele, ulemper og producentoplysninger.Katalog

Hvad er LFEC3E-3Q208C?

De LFEC3E-3Q208C er en omkostningseffektiv feltprogrammerbar portarray (FPGA) fra Lattice Semiconductor, designet som en del af familien Latticeec (økonomi).Denne familie blev udviklet til at levere programmerbare logiske løsninger, der afbalancerer overkommelige priser med pålidelig ydelse til mainstream -design.Inden for Gatticeec-hierarkiet sidder det i mellemområdet og tilbyder omkring 3.000 logiske elementer og effektiv strømforbrug og brodørger mellemrummet mellem mindre indgangsenheder og større, mere ressourceintensive modeller.Den bredere GittericeCP/EC-serie understreger lave omkostninger programmerbarhed, skalerbarhed og fleksibilitet på tværs af flere enhedsstørrelser, hvor EC-varianten fokuserer på økonomidrevet ydeevne.

Leder du efter LFEC3E-3Q208C?Kontakt os for at kontrollere den aktuelle lager, ledetid og prisfastsættelse.

LFEC3E-3Q208C-funktioner

• Logiske ressourcer

Enheden integrerer ca. 3.100 logiske elementer organiseret i 384 blokke, hvilket giver den nok kapacitet til mellemklasse-design.Denne ressourcebalance gør den velegnet til kontrollogik, signalbehandling og indlejrede applikationer uden for store omkostninger.

• Programmerbar I/O.

Med op til 145 programmerbare input/output -stifter understøtter det en lang række tilslutningsmuligheder.Disse I/OS er kompatible med flere standarder såsom LVCMO'er, LVTTL, LVDS, PCI og SSTL, hvilket muliggør fleksibel systemintegration.

• Indlejret hukommelse

FPGA inkluderer dedikeret blokram (EBR) og distribuerede RAM-ressourcer, der giver effektiv opbevaring på chip.Dette gør det muligt at implementere databuffering, opslagstabeller eller små indlejrede minder direkte inde i enheden.

• Urstyring

Den har op til fire integrerede PLL'er, der tilbyder frekvensmultiplikation, opdeling og faseforskydning.Dette muliggør præcis timingkontrol og synkronisering for højhastighedsdesign.

• DDR -hukommelsesstøtte

Enheden inkluderer hardwarestøtte til DDR -grænseflader, der er i stand til at køre DDR400 (200 MHz).Dette gør det praktisk for design, der kræver ekstern hukommelsesadgang med ekstern hukommelse.

• Strømeffektivitet

I drift med en 1,2 V kerneforsyning minimerer FPGA det samlede systemkraftforbrug.Dets design med lav effekt er ideel til bærbare eller energisensitive applikationer.

• Funktioner på systemniveau

Indbyggede funktioner såsom IEEE 1149.1 Boundary Scan, On-Chip Logic Analysis (ISPTracy) og en SPI Boot Flash-interface-forenkling af test og fejlsøgning.Disse funktioner reducerer udviklingstiden og forbedrer designpålideligheden.

• Udviklingsstøtte

Understøttet af Ispleever Design Suite drager enheden fordel af automatiseret syntese, sted-og-vej- og verifikationsværktøjer.Du kan også bruge isplevercore IP-blokke til at fremskynde fælles funktioner og forkorte tid til markedet.

GittericeCP/EF Familieblokdiagram

Blokdiagrammet for LatticeECP/EC-familien (inklusive LFEC3E-3Q208C) viser, hvordan FPGA er bygget, og hvordan dens dele fungerer sammen.De programmerbare I/O -celler (billeder) anbringes omkring kanterne for at forbinde chippen med udvendige enheder, der understøtter mange signalstandarder.Inde i håndterer de programmerbare funktionelle enheder (PFUS) logiske operationer med nogle parret til indlejret blokram (EBR) til lagring af data og andre kun fokuseret på logik.Sysclock PLLS administrerer ursignaler, så designet kan køre med den rigtige hastighed og timing.Sysconfig -porten og JTAG -porten lader dig programmere, test og debug FPGA let.Dette layout giver LFEC3E-3Q208C fleksibilitet, pålidelig ydelse og enkel integration i omkostningsfølsomme design.

GitterICP/EC Sive Diagram

Skiven i LatticeECP/EF-familien, som i LFEC3E-3Q208C, er den centrale logiske enhed, der kombinerer LUT4 & bærer blokke til udførelse af logik og aritmetiske operationer.Hver skive inkluderer også flip-flops/låse til at gemme data og muliggøre sekventiel logik, med multiplexere til at rute signaler fleksibelt enten gennem registre eller direkte.Denne struktur er vigtig, fordi den giver FPGA -hastighed, fleksibilitet og effektivitet til at håndtere både enkle og komplekse digitale design.Følgende tabel opsummerer skivesignalbeskrivelserne, inklusive deres funktioner, typer, signalnavne og formål.

|

Fungere |

Type |

Signalnavne |

Beskrivelse |

|

Input |

Datasignal |

A0, B0, C0, D0 |

Input til LUT4 |

|

Input |

Datasignal |

A1, B1, C1, D1 |

Input til LUT4 |

|

Input |

Multi-purpose |

M0 |

Multipurpose input |

|

Input |

Multi-purpose |

M1 |

Multipurpose input |

|

Input |

Kontrolsignal |

Ce |

Ur aktivere |

|

Input |

Kontrolsignal |

LSR |

Lokalt sæt/nulstilling |

|

Input |

Kontrolsignal |

CLK |

Systemur |

|

Input |

Inter-PFU signal |

Fcin |

Hurtig bær i¹ |

|

Produktion |

Datasignaler |

F0, F1 |

LUT4 Output Register Bypass Signals |

|

Produktion |

Datasignaler |

Q0, Q1 |

Registrer output |

|

Produktion |

Datasignaler |

Ofx0 |

Output fra en LUT5 MUX |

|

Produktion |

Datasignaler |

Ofx1 |

Output af en LUT6, LUT7, LUT8 2 MUX Afhængigt af skiven |

|

Produktion |

Inter-PFU signal |

FCO |

For den rigtige mest PFU den hurtige bære kæde output¹ |

LFEC3E-3Q208C-specifikationer

|

Type |

Parameter |

|

Fabrikant |

Gitter Semiconductor |

|

Spænding - Forsyning |

1.14V ~ 1.26V |

|

Samlede rambits |

56.320 |

|

Leverandørenhedspakke |

208-PQFP (28x28) |

|

Serie |

Ec |

|

Pakke / sag |

208-BFQFP |

|

Pakke |

Bakke |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Antal logiske elementer/celler |

3.100 |

|

Antal I/O. |

145 |

|

Monteringstype |

Overflademontering |

|

Basisproduktnummer |

LFEC3 |

LFEC3E-3Q208C-applikationer

1. indlejrede kontrolsystemer

LFEC3E-3Q208C er velegnet til indlejrede controllere i enheder, industriel automatisering og IoT-gateways.Dens moderate logikdensitet og lave omkostningsdesign giver mulighed for at erstatte fastfunktionslogik med programmerbar fleksibilitet.Dette gør det lettere at opgradere systemer eller tilpasse sig udviklende standarder uden at redesigne hardware.

2. DDR -hukommelsesgrænseflade

Med indbygget support til DDR400-hukommelse kan enheden administrere databuffering, logning eller midlertidig opbevaring i applikationer.Denne funktion er nyttig i systemer, hvor ekstern hukommelseshastighed er vigtig, men fuld high-end FPGA-ydelse er ikke påkrævet.Mange drager fordel af en balance mellem hastighed, omkostninger og hukommelseseffektivitet.

3. I/O Bridging and Protocol Conversion

Takket være sin brede støtte til I/O -standarder som LVCMO'er, LVTTL, LVDS, PCI og SSTL er FPGA effektiv til at bygge bro mellem forskellige digitale grænseflader.Det kan konfigureres til at oversætte signaler mellem delsystemer, hvilket gør det værdifuldt i blandet-teknologi-design.Denne fleksibilitet hjælper med at udvide levetiden for eksisterende hardware ved at muliggøre kompatibilitet med nye komponenter.

4. Industrielle og infrastrukturapplikationer

Enheden kan også tjene i omkostningsfølsomme industrielle og infrastrukturudstyr, hvor pålidelighed og moderat ydeevne er tilstrækkelig.Dens støtte til grænsescanning, fejlfinding på chip og lav effekt gør det ideelt til systemer, der kræver effektivitet og let vedligeholdelse.Typiske roller inkluderer kontrolenheder, interfacemoduler og overvågningssystemer.

LFEC3E-3Q208C Lignende dele

|

Specifikation |

LFEC3E-3Q208C |

LFEC3E-3Q208I |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

Logiske elementer (LUTS) |

~ 3.1k |

~ 3.1k |

~ 3.1k |

~ 3.1k |

~ 1,5k |

~ 6.1k |

|

Logikblokke |

384 |

384 |

384 |

384 |

192 |

768 |

|

Embedded Block Ram (EBR) |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 18 kb |

~ 92 kb |

|

Maksisk driftsfrekvens |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 300 MHz |

~ 340 MHz |

|

I/O -tælling |

145 |

145 |

145 |

145 |

112 |

145 |

|

Pakke |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

|

Kerne spænding |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

|

Temperaturområde |

0 ° C til +70 ° C. |

–40 ° C til +85 ° C. |

0 ° C til +70 ° C. |

0 ° C til +70 ° C. |

0 ° C til +70 ° C. |

0 ° C til +70 ° C. |

|

Overholdelse / pakketype |

Standard |

Industriel |

Lead-Free (QN) |

Variant (Q) |

Standard |

Standard |

|

Anvendelse |

Mid-densitet, generel formål |

Samme som LFEC3E men industriel brug |

Samme som LFEC3E, men pakken kompatibel |

Samme familie, let migration |

Optidsomkostningsindstilling med lav densitet |

Opgradering med højere densitet |

LFEC3E-3Q208C-programmeringstrin

Inden du begynder at programmere LFEC3E-3Q208C, er det vigtigt at forberede de rigtige værktøjer og forstå strømmen af design til enhedskonfiguration.Hvert trin bygger på det foregående, så omhyggelig opmærksomhed vil sikre en jævn programmeringsproces.

1. Forbered programmeringshardware og software

Du starter med at installere Lattice's Diamond Programmer eller ISPVM -system, som er de officielle værktøjer til denne FPGA.Indstil derefter JTAG-programmeringskablet, såsom HW-USBN-2B, og sørg for, at driverne er korrekt installeret.Dette trin sikrer, at din computer er klar til at kommunikere med målenheden uden forbindelsesfejl.

2. Implementere dit design i udviklingssoftware

Opret derefter et nyt projekt i Lattice Diamond og vælg LFEC3E-3Q208C som din målenhed.Derefter tilføjer du dine Verilog- eller VHDL -kildefiler, anvender pinopgaver og definerer eventuelle timingbegrænsninger.Når det er gjort, syntetiserer du designet, udfører sted-og-route og genererer til sidst de bitstream-fil (.bit eller .JED), der vil blive brugt til programmering.

3. Opret brættet og forbindelserne

Tilslut nu JTAG -kablet til dit FPGA -kort, og sørg for, at jordforbindelsen er sikker, før du vedhæfter signallinjerne.Bekræft, at pull-up- og pull-down-modstande er korrekt på plads, især på TCK- og åbne drænelinjer.Hvis dit bord har yderligere kontrolstifter som Slet eller ISPEN, skal du konfigurere dem korrekt for at forhindre utilsigtede nulstillinger under programmering.

4. programmer enheden

Med hardware klar, skal du starte programmeringsværktøjet og vælge dit tilsluttede kabel.Indlæs den genererede bitstream -fil, og vælg den relevante tilstand, normalt JTAG, afhængigt af din opsætning.Start programmeringsprocessen, og værktøjet konfigurerer FPGA, mens de bekræfter, at dataene er blevet korrekt skrevet.

5. Kontroller og debug konfigurationen

Efter programmering skal du kontrollere de udførte eller init -stifter på dit bord for at bekræfte, at FPGA har konfigureret med succes.Brug om nødvendigt ISPTracy -logikanalysatoren eller grænsescanningsfunktionerne til at teste funktionalitet og validere signaladfærd.Du kan gentage design- og programmeringscyklus, når der kræves ændringer, hvilket sikrer, at dit projekt raffineres trin for trin.

LFEC3E-3Q208C fordele og ulemper

Fordele

• Lavt strømforbrug, der er egnet til energisensitive design

• Omkostningseffektiv sammenlignet med FPGA'er med højere ende

• Enkel værktøjskæde med lettere indlæringskurve

• Feltekonfigurerbar for opdateringer efter implementering

• Kompakt pakke med god balance mellem ressourcer

Ulemper

• Begrænset ydelse sammenlignet med større FPGA'er

• Lavere logik og hukommelseskapacitet end high-end-enheder

• Færre tredjeparts IP-kerner og økosystemstøtte

• Værktøjskæde mangler avancerede funktioner hos større leverandører

• Ikke egnet til ultrahøjhastighedsgrænseflader

LFEC3E-3Q208C Emballagedimensioner

|

Type |

Parameter |

|

Pakningstype |

208-PQFP (Plastic Quad Flat Package) |

|

Kropsstørrelse |

28 mm × 28 mm |

|

Pitch |

0,5 mm |

|

Pakkehøjde (max) |

~ 3,4 mm |

|

Blyantal |

208 stifter |

|

Pakningstil |

Gull-Wing Leads (Quad) |

|

Monteringstype |

Overflademontering |

|

Sagskode |

BFQFP-208 |

|

Leverandørpakke |

Bakke |

LFEC3E-3Q208C Producent

LFEC3E-3Q208C er fremstillet af Gitter Semiconductor Corporation , et U.S.-baseret selskab med hovedkvarter i Hillsboro, Oregon.Grundlagt i 1983 er Lattice specialiseret i udvikling af lav effekt, omkostningseffektivt feltprogrammerbare gatearrays (FPGA'er) og relaterede løsninger.Virksomheden fokuserer på at muliggøre applikationer inden for kommunikation, computing, forbrugerelektronik, industrielle og bilmarkeder.Gitter, der er kendt for sin innovation inden for energieffektive programmerbare enheder, har etableret sig som en nøglespiller i FPGA-branchen, især for design, der kræver kompakte formfaktorer, reduceret strømforbrug og høj pålidelighed.

Konklusion

LFEC3E-3Q208C tilbyder en god blanding af lave omkostninger, brug af lav effekt og nok logik og hukommelse til mellemklasseprojekter.Det understøtter mange I/O-standarder, har indbygget RAM og PLL'er og kan arbejde med DDR400-hukommelse, hvilket gør det nyttigt til kontrol, interface og industrielle opgaver.Programmering er enkel med gitterværktøjer og ekstra fejlfindingsfunktioner hjælp til test.Selvom det ikke kan matche hastigheden og kapaciteten for større FPGA'er, er det et pålideligt valg for design, der har brug for fleksibilitet, effektivitet og overkommelig ydelse.

Datablad PDF

LFEC3E-3Q208C Datablad:

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. understøtter LFEC3E-3Q208C højhastighedsgrænseflader som PCIe eller Gigabit Ethernet?

Nej. LFEC3E-3Q208C er designet til mainstream og omkostningsfølsomme applikationer, så det inkluderer ikke indfødte højhastigheds-serielle transceivere.Det fokuserer i stedet på parallelle grænseflader og DDR -hukommelsesstøtte.

2. kan LFEC3E-3Q208C omprogrammeres efter implementering?

Ja.Som FPGA er LFEC3E-3Q208C fuldt konfigurerbar, hvilket tillader opdateringer og designændringer, selv efter implementering.Denne fleksibilitet reducerer de langsigtede vedligeholdelsesomkostninger og udvider produktets levetid.

3. Hvordan håndterer LFEC3E-3Q208C-fejlfinding og test?

Enheden integrerer grænsescanning (IEEE 1149.1), on-chip-logisk analyse (ISPTRACY) og SPI Boot Flash-support.Disse indbyggede værktøjer forenkler debugging og reducerer behovet for ekstern testhardware.

4. kan LFEC3E-3Q208C udvide levetiden for ældre hardwaresystemer?

Ja, takket være dens brede I/O -kompatibilitet og protokolbrofunktioner kan det interface ældre systemer med nyere komponenter, hvilket hjælper virksomheder med at udvide nytten af eksisterende hardware.

5. Hvilke programmeringsværktøjer kræves til LFEC3E-3Q208C?

Det er programmeret ved hjælp af Lattice's Diamond Programmør eller ISPVM -system.Disse værktøjer understøtter designindgang, bitstream -generation og enhedskonfiguration, hvilket gør arbejdsgangen strømlinet.

AD73311LARS: datablad, funktioner, pinout og programmeringsvejledning

på 2025-08-28

EPM1270F256C4N MAX II CPLD Oversigt: Funktioner, specifikationer og applikationer

på 2025-08-28

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-19 147782

-

USB-C pinout og funktioner

på 2000-04-19 112070

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-19 111352

-

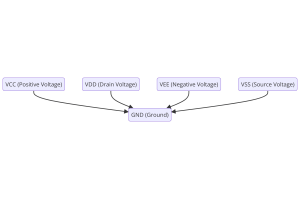

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-19 83829

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79642

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 67006

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63131

-

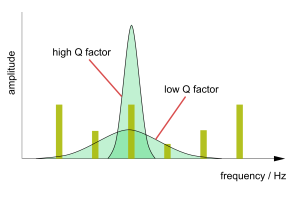

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63067

-

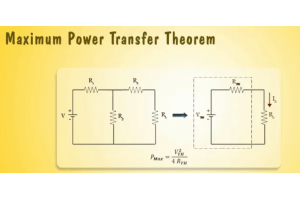

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52225