XC2S50-5TQG144I FPGA: funktioner, specifikationer, applikationer og programmeringsvejledning

XC2S50-5TQG144I er en fleksibel og kraftfuld FPGA (feltprogrammerbar portarray) fra AMD Xilinx's Spartan-II-familie.Det er designet til digitale projekter, der har brug for tilpasning, hastighed og pålidelighed.Denne guide forklarer funktionerne, specifikationerne, programmeringsprocessen og anvendelser af denne FPGA til at hjælpe dig med at forstå, hvordan du får mest muligt ud af det.Katalog

XC2S50-5TQG144I Oversigt

De XC2S50-5TQG144I er en spartansk-II FPGA fra AMD Xilinx, designet til digitale projekter, der har brug for fleksibilitet og ydeevne.Det har 50.000 systemporte og 1.728 logiske celler, hvilket gør det muligt for det at håndtere komplekse opgaver.Chippen inkluderer 384 konfigurerbare logiske blokke (CLBS) og 32.768 RAM -bits, hvilket giver den god hukommelse og behandlingseffekt.Med 92 input/output (I/O) stifter kan det let oprette forbindelse til andre komponenter.Det kommer i en 144-polet tynd quad flad pack (TQFP), som er kompakt og let at bruge.FPGA kører på 2,5V (med et sikkert interval på 2,375V til 2,625V) og fungerer godt i temperaturer mellem -40 ° C og +100 ° C.Denne spartanske-II FPGA er lavet med 0,18-mikron-teknologi, hvilket gør den effektiv og pålidelig.Det er programmerbar, hvilket betyder, at du kan opdatere dens funktioner efter behov.

For en omkostningseffektiv, højtydende løsning, er det at placere en bulkordre hos os det optimale valg, hvilket sikrer overlegen kvalitet.

XC2S50-5TQG144I CAD-modeller

XC2S50-5TQG144I Symbol

XC2S50-5TQG144I Fodaftryk

XC2S50-5TQG144I 3D-model

XC2S50-5TQG144I Funktioner

• Systemporte: XC2S50-5TQG144I FPGA tilbyder cirka 50.000 systemporte.Dette gør det muligt for det at understøtte komplekse digitale design og applikationer, der kræver en betydelig mængde af logiske behandlingsfunktioner.

• Logiske celler: Denne enhed inkluderer 1.728 logiske celler, der letter implementeringen af komplicerede logiske konfigurationer og skaber forskellige digitale funktionaliteter inden for FPGA.

• Konfigurerbare logiske blokke (CLBS): Den har 384 konfigurerbare logiske blokke (CLBS), der giver grundlaget for FPGA's logik.Disse blokke kan programmeres og rekonfigureres for at imødekomme specifikke designkrav, hvilket forbedrer enhedens samlede alsidighed.

• VÆDDER: FPGA er udstyret med 32.768 bit af intern RAM, der tilbyder effektiv datalagrings- og hentningskapacitet til opgaver, der involverer datamanipulation og midlertidig datalagring.

• I/O -stifter: Med 92 I/O-stifter sikrer XC2S50-5TQG144I rigelig ekstern forbindelse, hvilket gør det muligt for det at interface med andre enheder og komponenter i et system til omfattende systemintegration.

• Driftsspænding: Enheden fungerer med en nominel spænding på 2,5V med et acceptabelt interval fra 2.375V til 2.625V.Dette spændingsområde hjælper med at sikre stabil drift og pålidelig ydelse under forskellige elektriske forhold.

• Temperaturområde: XC2S50-5TQG144I er designet til at fungere effektivt i et bredt temperaturområde, fra -40 ° C til +100 ° C, hvilket gør det velegnet til implementering i miljøer med udfordrende termiske forhold.

XC2S50-5TQG144I blokdiagram

Diagrammet viser, hvordan signaler bevæger sig ind og ud af XC2S50-5TQG144I FPGA.Det forklarer, hvordan chip håndterer input- og output -signaler til at kommunikere med andre komponenter.På Output side , signaler kommer inde fra FPGA og går gennem opbevaringsenheder kaldet flip-flops.Disse flip-flops holder data og sørger for, at signaler ændres på det rigtige tidspunkt.Signalerne passerer derefter gennem en programmerbar outputbuffer, der justerer, hvor stærkt signalet er, og kontrollerer, hvor hurtigt det ændrer sig.Der er også en switch (OE -kontrol), der beslutter, om output skal være aktiv eller holde sig væk.Et beskyttelseskredsløb forhindrer skader på grund af statisk elektricitet, før signalet når I/O -stifterne, der opretter forbindelse til andre enheder.På input side, signaler udefra kommer ind gennem den programmerbare inputbuffer, der behandler dem, før de sender dem inde i FPGA.En programmerbar forsinkelsesenhed hjælper med at justere signal -timing, så alt forbliver synkroniseret.FPGA kan også bruge en intern referencespænding (VREF) til at matche forskellige spændingsniveauer, hvilket gør det lettere at arbejde med forskellige typer kredsløb.Nogle I/O -stifter deler denne spændingsreference for at holde signaler stabile.Dette design hjælper FPGA med at styre signaler effektivt, hvilket sikrer korrekt timing, beskyttelse og kompatibilitet med forskellige elektroniske komponenter.

XC2S50-5TQG144I-specifikationer

|

Type |

Parameter |

|

Fabrikant |

AMD Xilinx |

|

Serie |

Spartan®-II |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Antal laboratorier/CLB'er |

384 |

|

Antal logiske elementer/celler |

1728 |

|

Samlede rambits |

32.768 |

|

Antal I/O. |

92 |

|

Antal porte |

50.000 |

|

Spænding - Forsyning |

2.375V ~ 2.625V |

|

Monteringstype |

Overflademontering |

|

Driftstemperatur |

-40 ° C ~ 100 ° C (TJ) |

|

Pakke / sag |

144-LQFP |

|

Leverandørenhedspakke |

144-tqfp (20x20) |

|

Basisproduktnummer |

XC2S50 |

XC2S50-5TQG144I applikationer

Indlejrede systemer

I indlejrede systemer giver XC2S50-5TQG144I den nødvendige logik til mikrokontrollerbaserede applikationer.Det bruges i vid udstrækning i bilelektronik, bærbare enheder og småskala robotik for at forbedre funktionalitet og lydhørhed.

Signalbehandling

FPGA udmærker sig i signalbehandlingsopgaver, hvor dens evne til at udføre parallel behandling er påkrævet.Det er ideelt til lyd- og videobehandling, telekommunikation og dataanalyse, der giver hestekræfter til at håndtere komplekse algoritmer og højhastighedsdatabrømme.

Industrielle kontrolsystemer

Industrielle kontrolsystemer drager fordel af denne FPGAs robusthed og programmerbarhed, hvilket gør den velegnet til applikationer såsom processtyring, maskinautomation og systemovervågning.Dens pålidelighed sikrer ensartet ydelse i miljøer, der kræver præcision og operationel stabilitet.

Kommunikationssystemer

I kommunikationssystemer hjælper XC2S50-5TQG144I med at styre datatransmission og modtagelse, understøttende aktiviteter såsom signalmodulation og demodulering, protokolkonvertering og netværksrutning.Dets tilpasningsevne er nøglen til at udvikle telekommunikationsinfrastrukturer og nye trådløse teknologier.

Prototype og udvikling

FPGA bruges også i vid udstrækning til prototype digitale kredsløb.Mange bruger det til at teste og forfine deres ideer inden den endelige produktion, især i komplekse ASIC- og brugerdefinerede chipdesignprojekter.Denne kapacitet reducerer udviklingstiden og -omkostningerne og fremskynder stien fra koncept til marked.

XC2S50-5TQG144I lignende dele

XC2S50-5TQG144I fordele

Omkostningseffektivitet

XC2S50-5TQG144I skiller sig ud for sin overkommelige pris og leverer flere funktioner pr. Dollar end mange konkurrerende FPGA'er.Denne omkostningseffektivitet opnås gennem avanceret processteknologi og en effektiv arkitektur, hvilket muliggør bredere implementering på omkostningsfølsomme markeder.

Høj ydeevne I/O og emballage

Denne FPGA understøtter en lang række I/O-standarder og fås i forskellige omkostningseffektive emballagemuligheder.Disse funktioner sikrer, at enheden kan integreres i flere applikationer uden at ofre ydeevne, hvilket gør den ideel til både avancerede og volumendrevne markeder, hvor interface-alsidighed og fysiske begrænsninger er faktorer.

Funktioner på systemniveau

Udstyret med avancerede hukommelsesstyringsfunktioner såsom distribueret RAM og konfigurerbar blok RAM, forbedrer XC2S50-5TQG144I databehandlingseffektiviteten.Disse funktioner letter kompleks datalagrings- og behandlingsopgaver, hvilket øger systemets samlede ydelse og skalerbarhed.

Omprogrammabilitet

Omprogrammabiliteten af XC2S50-5TQG144I tillader ubegrænsede ændringer af dens konfiguration, hvilket er fordelagtigt i udviklingsfasen.Denne fleksibilitet gør det muligt for at forfine design gennem iterative opdateringer uden yderligere hardwareomkostninger, fremme innovation og reducere tid til slutproduktet.

XC2S50-5TQG144I Programmeringstrin

Programmering af XC2S50-5TQG144I FPGA fra AMD Xilinx's Spartan-II-serie involverer en struktureret række trin designet til effektivt at oversætte et digitalt design til en funktionel FPGA-konfiguration.Her er en integreret og detaljeret guide til at hjælpe dig gennem programmeringsprocessen:

1. Designindgang

Begynd med designindgangsfasen, hvor du opretter din digitale logik ved hjælp af et hardwarebeskrivelsessprog (HDL), såsom VHDL eller Verilog.Dette indledende trin involverer detaljer om den funktionalitet og logik, du vil implementere i FPGA.Det kræves, at dit design er præcist og nøjagtigt repræsenterer de tilsigtede operationer for at sikre en vellykket syntese og implementering.

2. Syntese

I syntese trin skal du bruge et synteseværktøj til at konvertere din HDL -kode til en netlist.En netlist er en sammenbrud af dit design i et format, der inkluderer forskellige sammenkoblede logiske elementer såsom porte og flip-flops.Denne proces oversætter dit teoretiske design til en praktisk plan, som FPGA kan forstå og implementere.

3. Implementering

Implementering involverer flere undertrin: kortlægning, placering og routing.Kortlægning tildeler elementerne i din netlist til specifikke logiske blokke inden for FPGA.Placering bestemmer de fysiske placeringer af disse blokke på FPGA -chippen for at optimere ydeevne og ressourceudnyttelse.Routing forbinder disse blokke gennem FPGAs programmerbare sammenkoblingsressourcer.Denne fase sikrer, at designet opfylder alle fysiske og præstationsbegrænsninger.

4. Definition af begrænsning

Under designprocessen er det nødvendigt med at definere begrænsninger.Begrænsninger guider implementeringsværktøjerne ved at specificere krav, såsom timing (hvor hurtigt FPGA skal betjene) og pin -opgaver (som stifter på FPGA vil oprette forbindelse til forskellige dele af din hardware).Disse er artikuleret i en brugerbegrænsningsfil (UCF), hvilket hjælper med at finjustere designet til at opfylde specifikke operationelle standarder.

5. Bitstream -generation

Når dit design med succes passerer gennem implementeringsfasen, er det næste trin at generere en Bitstream -fil.Denne fil indeholder alle de konfigurationsdata, som FPGA har brug for for at udføre designet.Bitstream er den endelige output af programmeringsprocessen, der repræsenterer den komplette, programmerede tilstand af FPGA.

6. Enhedsprogrammering

Det sidste trin er at indlæse bitstream i XC2S50-5TQG144I FPGA, som kan gøres ved hjælp af forskellige konfigurationstilstande afhængigt af din opsætning.I Master seriel tilstand, FPGA læser autonomt konfigurationsdataene fra en vedhæftet seriel prom (programmerbar skrivebeskyttet hukommelse). Slave seriel tilstand Tillader en ekstern masterenhed, såsom en mikrokontroller, at fodre FPGA -konfigurationsdata serielt. Slave parallel tilstand Aktiverer højhastighedsprogrammering ved at levere konfigurationsdata parallelt fra en ekstern masterenhed.Til sidst, Boundary Scan (JTAG) -tilstand Anvender JTAG -interface til både programmering og test, hvilket gør den nyttig under udvikling til iterativ fejlfinding og verifikation.

XC2S50-5TQG144I Emballagedimensioner

The XC2S50-5TQG144I er en feltprogrammerbar portarray (FPGA) fra Xilinx's Spartan-II-familie, der ligger i en 144-polet tynd Quad Flat Pack (TQFP) pakke.Denne pakke måler 20 mm x 20 mm.

XC2S50-5TQG144I Producent

XC2S50-5TQG144I er en FPGA fra Spartan-II-familien, fremstillet af AMD Xilinx.Xilinx, nu en del af AMD, er et førende halvlederfirma, der specialiserer sig i FPGA'er, adaptive SOC'er og andre programmerbare logiske enheder.XC2S50-5TQG144I blev oprindeligt udviklet under Xilinx Spartan-II-serien, der tilbyder 50.000 systemporte og 1.728 logiske celler, designet til højtydende, men alligevel omkostningseffektive applikationer.Med Xilinxs erhvervelse af AMD støtter virksomheden fortsat ældre produkter som Spartan-II-serien, mens de fremmer nyere FPGA-arkitekturer.Imidlertid er XC2S50-5TQG144I en ældre generation af FPGA og kan stå over for eventuel forældelse, når AMD Xilinx skifter fokus til mere avancerede FPGA-familier.

Konklusion

XC2S50-5TQG144I FPGA er en omkostningseffektiv og omprogrammerbar chip, der tilbyder god ydelse og fleksibilitet.Det er vidt brugt i indlejrede systemer, industrielle maskiner og kommunikationsnetværk på grund af dets højhastighedsbehandling og stærke tilslutningsmuligheder.Med sin evne til at blive programmeret og opdateret hjælper denne FPGA med at teste og udvikle nye ideer inden den endelige produktion.Selvom nyere FPGA'er er tilgængelige, forbliver denne model et solidt valg til projekter, der har brug for en pålidelig og overkommelig FPGA -løsning.Denne vejledning giver en klar og enkel oversigt over FPGAs funktioner, anvendelser og programmeringsproces, hvilket gør det til en værdifuld ressource for alle.

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Kan jeg bruge XC2S50-5TQG144I til højhastighedsapplikationer?

XC2S50-5TQG144I understøtter hastigheder op til 200 MHz, hvilket gør det velegnet til de fleste indlejrede og industrielle applikationer.Men hvis dit projekt kræver højhastighedsgrænseflader som PCIe eller DDR-hukommelse, har du muligvis brug for en mere avanceret FPGA som Spartan-6 eller Artix-7-serien.

2. Hvordan sammenlignes XC2S50-5TQG144I med den nyere Spartan-3 eller Spartan-6 FPGA'er?

Mens nyere FPGA'er som Spartan-3 eller Spartan-6 tilbyder forbedret ydelse, højere logikdensitet og yderligere funktioner, forbliver XC2S50-5TQG144I et foretrukket valg for omkostningsfølsomme projekter med moderat kompleksitet.Hvis du har brug for arvekompatibilitet eller en stabil forsyningskæde, er XC2S50-5TQG144I en fantastisk mulighed.

3. Hvilke programmeringsværktøjer er kompatible med XC2S50-5TQG144I FPGA?

XC2S50-5TQG144I programmeres ved hjælp af Xilinx ISE (Integrated Software Miljø).Mens nyere Xilinx-værktøjer som Vivado ikke understøtter Spartan-II-familien, giver ISE alt det nødvendige design, syntese og programmeringsfunktionaliteter til denne FPGA.

4. kan jeg migrere et eksisterende Spartan-II-design til en nyere FPGA?

Ja, men det kræver ændringer.De nyere Spartan-3- og Spartan-6-familier bruger forskellige arkitektur, spændingsniveauer og konfigurationsmetoder.Hvis du overvejer migration, kan vi hjælpe med at vælge passende alternativer og minimere designændringer.

5. Understøtter XC2S50-5TQG144I JTAG-programmering?

A: Ja, FPGA understøtter JTAG (IEEE 1149.1) Boundary Scan -programmering, som tillader let fejlfinding og konfiguration ved hjælp af en standard JTAG -interface.Dette er nyttigt til både indledende programmering og rekonfiguration uden ekstern hukommelse.

XC4013XL-3PQ240C FPGA: Alternativer, specifikationer, applikationer og datablad

på 2025-03-18

RF -strømforstærkere: Hvordan de fungerer, hvilken type er mere effektiv

på 2025-03-18

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-19 147782

-

USB-C pinout og funktioner

på 2000-04-19 112070

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-19 111352

-

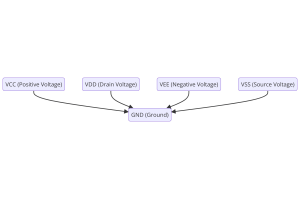

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-19 83829

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79642

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 67006

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63131

-

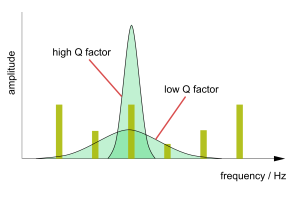

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63067

-

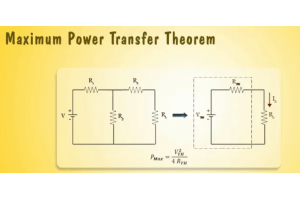

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52225