XCV200-6FG456C FPGA: Funktioner, specifikationer, programmering og applikationer

XCV200-6FG456C er en kraftfuld FPGA (Field-Progromble Gate Array) fra AMD Xilinx Virtex®-serien.Denne guide forklarer dens funktioner, pin -layout, programmeringstrin og anvendelser.Med høje behandlingseffekt, fleksible designmuligheder og stærk input/output (I/O) kapacitet hjælper denne FPGA med at opbygge hurtige og pålidelige digitale systemer.Uanset om du arbejder på netværk, kontrolsystemer eller brugerdefineret elektronik, vil denne vejledning hjælpe dig med at forstå, hvordan XCV200-6FG456C kan bruges i dine projekter.Katalog

XCV200-6FG456C Oversigt

De XCV200-6FG456C er en bemærkelsesværdig model inden for AMD Xilinx Virtex® FPGA -familien, designet til at levere robuste programmerbare logiske løsninger til komplekse digitale systemer.Denne specifikke chip omfatter cirka 236.666 systemporte og har 1.176 konfigurerbare logiske blokke (CLBS) og 5.292 logiske celler.Det inkluderer også 57.344 samlede RAM-bits og understøtter 284 I/O-stifter, der ligger i en 456-ball Fine-Pitch Ball Grid Array (FBGA) -pakke, der måler 23 mm x 23mm.Denne model fungerer på en 2,5V nominel spænding med en rækkevidde på 2,375V til 2,625V og kan fungere inden for et temperaturområde fra 0 ° C til 85 ° C.Den bredere Virtex® -serie henvender sig til en række applikationer med densiteter fra 50.000 til over 1 million systemporte og systemurhastigheder på op til 200 MHz.Det understøtter mange I/O -standarder, herunder LVTTL, LVCMOS og PCI, blandt andre.Funktioner såsom forsinkelseslåste sløjfer (DLL'er), konfigurerbare logiske blokke med indlejret hukommelse og dedikeret bærelogik til aritmetiske operationer forbedrer dens funktionalitet.Virtex®-familien, der er fremstillet ved hjælp af en 0,22 um 5-lags metalproces, garanterer ydeevne og pålidelighed.

Hvis du ønsker at integrere top-tier FPGA-teknologi i dine produkter eller systemer, er det et smart træk at købe XCV200-6FG456C i bulk med os.Det opfylder industristandarder og holder dig foran fremtidige teknologiske behov.

XCV200-6FG456C-funktioner

• Systemporte: XCV200-6FG456C tilbyder cirka 236.666 systemporte.Denne høje portantal muliggør implementering af komplekse integrerede digitale logikkredsløb på en enkelt chip, hvilket forbedrer både ydelse og alsidighed i en række applikationer.

• Logiske ressourcer: Det inkluderer 1.176 konfigurerbare logiske blokke (CLBS) og 5.292 logiske celler.Disse ressourcer er gode til at designe fleksible og skalerbare digitale kredsløb.CLB'er kan programmeres til at udføre en lang række logiske funktioner, mens det store antal logiske celler muliggør håndtering af omfattende logiske operationer og processer.

• Hukommelse: Enheden leverer 57.344 bit RAM, fordelt mellem dens logiske blokke.Denne indlejrede RAM bruges til applikationer, der kræver hurtig og effektiv datalagring og hentning, hvilket understøtter højhastighedsdataoperationer integreret i moderne digitale systemer.

• I/O -kapaciteter: Med 284 input/output-stifter letter XCV200-6FG456C omfattende grænsefladefunktioner.Disse I/O -stifter understøtter forskellige signalstandarder og gør det muligt for FPGA at kommunikere effektivt med andre komponenter i et system, såsom hukommelsesenheder, processorer og perifere enheder.

• Spændings- og temperaturområde: Betjening med en nominel spænding på 2,5V, med et acceptabelt interval fra 2,375V til 2.625V, er denne FPGA designet til lavt effektforbrug, mens den opretholder robust ydeevne.Det kan fungere inden for et forbindelsestemperaturområde fra 0 ° C til 85 ° C, hvilket sikrer pålidelighed under forskellige miljøforhold.

XCV200-6FG456C PIN-funktionsdiagram

De XCV200-6FG456C PIN-funktionsdiagram er en struktureret repræsentation af FPGAs pin -opgaver, kategoriseret i forskellige banker (Bank 0 til bank 7).Hver bankgrupper stifter baseret på deres funktion og fysiske placering på FPGA -pakken.Nummererings- og mærkningssystemet følger et gittermønster, hvor rækker betegnes med bogstaver (A, B, C osv.) Og kolonner efter tal (1, 2, 3 osv.), Der letter hurtig identifikation af specifikke stifter.Disse banker svarer til forskellige input/output -funktioner, effekt, jord og dedikeret signalruting.Pins tildeles forskellige funktionelle grupperinger, herunder generel I/O (GPIO), ofte mærket som "G" (generel input/output), "V" (spændingsforsyning) og "O" (output).Strøm- og jordstifter er markeret tydeligt, hvilket sikrer stabil FPGA -drift.Specialformålstifter såsom urindgange, nulstillinger og kontrolsignaler identificeres med symboler som "R" eller "T."Nogle stifter tjener også dedikerede kommunikationsroller, herunder JTAG-konfiguration og højhastighedsur, til programmering og fejlsøgning.

XCV200-6FG456C-blokdiagram

Input/outputblok

Diagrammet repræsenterer Input/output blok (IOB) Struktur af XCV200-6FG456C FPGA, som er medlem af Xilinx Virtex-familien.Diagrammet viser nøgleelementer, der er involveret i input- og output -operationer, der fremhæver dataflyt og kontrolmekanismer.I kernen af diagrammet bruges tre D-flip-flops til at registrere signaler til input, output og tri-state-kontrol.Outputregisteret styres af OCE (Output Clock Enable) -signalet, der bestemmer, hvornår outputdataene er låst.Tilsvarende kontrolleres tri-state-registeret af TCE (Tri-State Clock Enable), der muliggør eller deaktivering af outputbufferen.Inputregisteret indfanger indgående data og anvender en programmerbar forsinkelse, før de overføres til den interne FPGA -logik gennem IBUF (inputbuffer).OBUFT (Tri-State Output Buffer) sikrer, at FPGA enten kan køre et signal på puden (I/O-pin) eller placere den i en højimpedanstilstand, afhængigt af kontrollogikken.Et svagt keeperkredsløb er inkluderet på puden for at opretholde den sidst kendte logiske tilstand, når der ikke er nogen aktiv driver, der forhindrer utilsigtede flydende forhold.Referencespændingen (VREF) bruges til visse inputstandarder, såsom SSTL eller HSTL, som kræver præcise spændingsniveauer for korrekt drift.Generelt tillader denne IOB-struktur FPGA at håndtere dataoverførsel med høj hastighed, understøtte forskellige I/O-standarder og give fleksibel kontrol over signaltiming og integritet.

Master/slave seriel tilstand

De Master/slave seriel tilstand Blokdiagram illustrerer konfigurationsprocessen for en Virtex FPGA, specifikt XCV200-6FG456C, når den er programmeret i en Daisy-Chain-konfiguration ved hjælp af en seriel EEPROM (XC1701L).I denne opsætning fungerer en virtex -enhed som master, der kontrollerer konfigurationsuret (CCLK) og serielt overfører konfigurationsdata til yderligere slave -FPGA'er i kæden.Master FPGA initierer konfigurationsprocessen ved at hævde programsignalet og nulstille alle enheder i kæden.Når initialiseringen er afsluttet, angiver init -signalet beredskab, og konfigurationsdata strømmer fra den serielle EEPROM (XC1701L) til DIN (data i) pin på master FPGA.Master FPGA læser data fra EEPROM og videresender dem gennem Dout (data ud) til efterfølgende slave -FPGA'er, hvilket synkroniserer dataoverførsel ved hjælp af CCLK -signalet.Det udførte signal bruges til at indikere vellykket konfiguration med en valgfri pull-up-modstand, der sikrer en stabil høj tilstand, når konfigurationen er afsluttet.XC1701L EEPROM styres af master FPGA ved hjælp af CLK, data, CE (ChIP Enable) og Nulstil/OE (Output Enable) -signaler, hvilket sikrer, at de lagrede konfigurationsdata korrekt hentes.Denne konfigurationsmetode er effektiv til programmering af flere FPGA'er ved hjælp af en enkelt EEPROM, hvilket reducerer ekstern ledningskompleksitet og sikrer, at alle enheder modtager synkroniserede konfigurationsdata.

XCV200-6FG456C-specifikationer

|

Type |

Parameter |

|

Fabrikant |

AMD Xilinx

|

|

Serie |

Virtex® |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Antal laboratorier/CLB'er |

1176 |

|

Antal logiske elementer/celler |

5292 |

|

Samlede rambits |

57344 |

|

Antal I/O. |

284 |

|

Antal porte |

236666 |

|

Spænding - Forsyning |

2.375V ~ 2.625V |

|

Monteringstype |

Overflademontering |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Pakke / sag |

456-BBGA |

|

Leverandørenhedspakke |

456-fbga (23x23) |

|

Basisproduktnummer |

XCV200 |

XCV200-6FG456C-applikationer

Telekommunikation og netværk

XCV200-6FG456C udmærker sig inden for telekommunikation og netværksapplikationer på grund af dets evne til at håndtere højhastighedsdatatransmissioner og komplekse signalbehandlingsopgaver.Dens høje portantal og robuste I/O -kapaciteter giver det mulighed for at understøtte funktioner såsom pakkebehandling, signalmodulation/demodulation og fejlkorrektionsprotokoller.

Digital Signal Processing (DSP)

Ideel til DSP -applikationer kan denne FPGA udføre hurtige og komplekse matematiske beregninger, der kræves i lyd- og videobehandlingsteknologier.Uanset om det er til multimediesystemer, stemmegenkendelse eller streamingtjenester, er XCV200-6FG456Cs kraftfulde behandlingsfunktioner og indlejret hukommelsesstøtte effektiv og højkvalitetssignalbehandling.

Industrielle kontrolsystemer

I den industrielle automatisering giver XCV200-6FG456C den nødvendige ydelse til styring af kontrolsystemer og automatiseringsnetværk.Dens evne til at udføre flere kontrolopgaver samtidig, mens det sikrer responstider, gør det velegnet til applikationer i processtyring, robotik og maskinvision.

Medicinske instrumenter

FPGA's præcision og hastighed er stor i medicinsk billeddannelse og diagnostisk udstyr, hvor det hjælper med behandlingen af komplekse algoritmer til billeddannelsesapplikationer såsom MRI, ultralyd og CT -scanninger.XCV200-6FG456Cs kapaciteter sikrer, at den kan håndtere høj data gennemstrømning og indviklet behandling, der kræves i moderne medicinsk teknologi.

XCV200-6FG456C lignende dele

XCV200-6FG456C-programmeringstrin

Programmeringstrin til XCV200-6FG456C:

1. Designindgang

Den indledende fase af FPGA -programmering involverer at definere din systems digitale logik og funktionalitet.Dette kan gøres ved hjælp af hardwarebeskrivelsessprog (HDL'er) såsom VHDL eller Verilog, hvor du skriver kode, der specificerer, hvordan FPGA behandler data og interagerer med anden hardware.Skematiske indgangsværktøjer, der er tilgængelige i FPGA -designsoftware som Xilinx ISE eller Vivado, kan bruges.Denne metode involverer at skabe en visuel repræsentation af logikken ved at trække og droppe komponenter, som nogle finder mere intuitive end at skrive kode.

2. Syntese

Når designet er afsluttet, er det næste trin syntese, hvor et værktøj som Xilinx's XST (Xilinx Synthesis Technology) omdanner din HDL -kode eller skematisk design til en netlist.Denne netlist beskriver kredsløbet med hensyn til generiske digitale komponenter, såsom logiske porte og registre.Synteseprocessen involverer også optimering af designet til at imødekomme ydelseskrav og minimere ressourceforbruget til effektiv FPGA -drift.

3. Implementering

Implementeringsprocessen begynder med oversættelse, der kombinerer dit design med begrænsningsfiler, der specificerer parametre såsom urfrekvenser og pinopgaver.Efter oversættelse tildeler kortlægningsfasen elementerne i din netlist til specifikke fysiske ressourcer på FPGA, ligesom opslagstabeller (LUTS) og flip-flops.Placerings- og routingfasen bestemmer derefter de fysiske placeringer af hver komponent inden for FPGAs arkitektur og etablerer forbindelserne mellem dem gennem programmerbare sammenkoblingsressourcer.Dette trin er fantastisk til at opnå de ønskede ydelsesmetrics, inklusive urfrekvenser.

4. Bitstream -generation

Efter vellykket placering og routing genererer værktøjet en Bitstream, en binær konfigurationsfil, der indeholder alle programmeringsoplysninger til FPGA.Det anbefales ofte at simulere den endelige design efter placering for at sikre, at bitstream opfører sig som forventet under forhold.Dette verifikationstrin hjælper med at undgå potentielle problemer under faktisk drift.

5. Konfiguration

Det sidste trin involverer at indlæse bitstream i FPGA ved hjælp af forskellige konfigurationsmetoder.Slave-seriel tilstand, en enkel og omkostningseffektiv mulighed, konfigurerer FPGA via en ekstern masterenhed, der sender data serielt.I master-seriel tilstand læser FPGA autonomt bitstream fra en tilknyttet seriel prom.For højhastighedskonfigurationer tillader SelectMap-tilstand en ekstern mikroprocessor at indlæse data hurtigt i FPGA.Derudover bruges JTAG-tilstand ikke kun til programmering, men også til test og fejlsøgning ved anvendelse af en standardgrænseflade til programmering i systemet og grænse-scanningstest.

XCV200-6FG456C fordele

Præstation

Xilinx Virtex-serien, som XCV200-6FG456C hører til, er optimeret til højhastighedsydelse og tilbyder systemurhastigheder på op til 200 MHz.Dette gør det velegnet til applikationer, der kræver hurtig databehandling, hvilket sikrer effektiv håndtering af komplekse algoritmer og højhastighedsoperationer som telekommunikation, behandling og multimedia.

I/O -standarder understøtter

Denne FPGA understøtter en lang række input/output -standarder, herunder LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT og AGP.Sådanne omfattende I/O-standarder understøtter XCV200-6FG456C til at integrere problemfrit med forskellige systemkomponenter, hvilket forbedrer dets anvendelighed på tværs af forskellige digitale økosystemer.Denne fleksibilitet giver mulighed for at tilpasse FPGA til forskellige grænsefladebetingelser uden systemændringer.

Urstyring

XCV200-6FG456C indeholder flere forsinkelseslåste sløjfer (DLL'er) til urfordeling og styring i systemet.Disse DLL'er hjælper med at forbedre systemets timing og pålidelighed ved at tilvejebringe præcise ursignaler, der er nødvendige for synkrone operationer.Denne funktion er vigtig for at reducere systemfejl og forbedre den samlede ydelse, især i komplekse design, der kræver nøjagtig timing og synkronisering.

Designfleksibilitet

Med 1.176 konfigurerbare logiske blokke og 5.292 logiske celler tilbyder XCV200-6FG456C betydelige logiske ressourcer med evnen til at implementere en bred vifte af funktionaliteter.Fra enkel limlogik til komplicerede digitale systemer understøtter denne FPGA komplekse designkrav, hvilket gør det ideelt til applikationer inden for brugerdefineret computing, digital signalbehandling og prototype.

Hurtig prototype

FPGA'er som XCV200-6FG456C er kendt for deres evne til at understøtte hurtig prototype.Denne enhed giver mulighed for hurtige design-iterationer og kan konfigureres i feltet, hvilket er en fordel for udviklingscyklusser, da det reducerer tid til marked.Det tilpasser sig også effektivt til at ændre krav eller opdateringer i projektspecifikationer, hvilket sikrer, at de endelige produkter er ajour med de nyeste teknologiske standarder.

Integrationsevne

Integrationsfunktionerne i XCV200-6FG456C letter konsolideringen af flere diskrete komponenter i en enkelt chip.Denne integration kan føre til reduceret systemkompleksitet, lavere strømforbrug og omkostningsbesparelser.Ved at minimere antallet af de nødvendige separate komponenter forenkler denne FPGA designprocesser og forbedrer pålideligheden og kompaktheden i det samlede system.

XCV200-6FG456C Emballagedimensioner

XCV200-6FG456C er en feltprogrammerbar Gate Array (FPGA) fra AMDs Virtex®-serie, der ligger i en 456-ball Fine-Pitch Ball Grid Array (FBGA) -pakke.

• Pakningstype: 456-fbga

• Pakningstørrelse: 23 mm x 23 mm

• Ball pitch: 1,0 mm

XCV200-6FG456C Producent

XCV200-6FG456C er en feltprogrammerbar Gate Array (FPGA), der oprindeligt blev udviklet af Xilinx, et firma, der er kendt for sit højtydende programmerbare logiske enheder.Efter Xilinx's erhvervelse af AMD, XCV200-6FG456C er nu forbundet med AMD som sin nuværende producent.Imidlertid er denne FPGA -model forældet og ikke længere i produktion.AMD understøtter fortsat nyere FPGA -arkitekturer med forbedret ydeevne, effekteffektivitet og udvidet levetid, hvilket gør moderne alternativer foretrukket til nye designs.

Konklusion

XCV200-6FG456C er en alsidig og højhastigheds FPGA, der er nyttig til mange teknologiapplikationer.Selvom det ikke længere foretages, er det stadig et godt valg for ældre systemer, der har brug for pålidelig ydelse.Denne guide har dækket sit design, programmeringstrin og praktisk anvendelse, hvilket gør det lettere at forstå, hvordan det fungerer, og hvordan det kan bruges.Når nyere FPGA'er bliver tilgængelige, kan du bruge denne viden til at vælge den rigtige FPGA til dine behov og forbedre digitale design.

Datablad PDF

XCV200-6FG456C Datablad:

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Hvad er strømforbruget i XCV200-6FG456C?

XCV200-6FG456C fungerer ved 2,5V med et spændingsområde fra 2,375V til 2.625V.Strømforbrug afhænger af logisk udnyttelse og urfrekvens, men som en ældre FPGA kan det være mindre effektive end nyere Xilinx-enheder.Korrekt strømstyring og varmeafledning bør overvejes.

2. Hvordan sammenlignes XCV200-6FG456C med XCV200-6FG256C?

XCV200-6FG456C har en større pakke (456-ball FBGA) sammenlignet med XCV200-6FG256C (256-ball FBGA), der tilbyder flere I/O-stifter (284 vs. 172) og potentielt bedre ydelse til applikationer, der kræver omfattende interface.Hvis dit design er afhængig af flere I/O-kapaciteter, er XCV200-6FG456C det bedre valg.

3. kan jeg omprogrammere XCV200-6FG456C flere gange?

Ja, XCV200-6FG456C er en SRAM-baseret FPGA, hvilket betyder, at den kan omprogrammeres et ubegrænset antal gange, så længe der leveres strøm.Du har dog brug for ekstern ikke-flygtig hukommelse (EEPROM eller FLASH) for at bevare bitstream efter en strømcyklus.

4. understøtter XCV200-6FG456C højhastigheds-seriel kommunikation?

XCV200-6FG456C understøtter flere I/O-standarder såsom LVTTL, LVCMOS, PCI, GTL, HSTL og SSTL, men det har ikke indbyggede højhastighedsser (serializer/deserializer) eller transceivere som moderne FPGA'er.For applikationer, der kræver serielle links med høj hastighed (f.eks. PCIe, Gigabit Ethernet eller HDMI), skal du overveje nyere FPGA-modeller.

5. Hvordan sammenligner XCV200-6FG456C med nyere FPGA-modeller?

XCV200-6FG456C hører til en ældre generation af FPGA'er.Sammenlignet med moderne Virtex FPGA'er har det et lavere gate -antal, langsommere urhastigheder og begrænset effekteffektivitet.Nyere modeller tilbyder højere logikdensitet, mere indlejret hukommelse, avancerede DSP -blokke og lavere strømforbrug, hvilket gør dem bedre til moderne applikationer.

AD73322AR pinout, funktioner og tekniske detaljer forklaret

på 2025-03-21

EP20K100EFC324-1X FPGA: Funktioner, specifikationer, applikationer og programmeringsvejledning

på 2025-03-20

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-19 147781

-

USB-C pinout og funktioner

på 2000-04-19 112056

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-19 111352

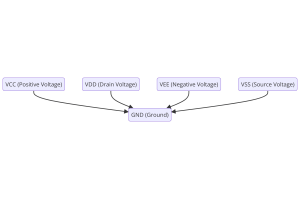

-

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-19 83810

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79622

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66994

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63118

-

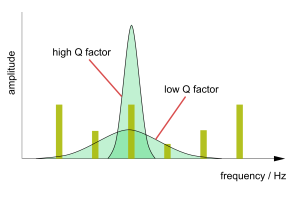

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63057

-

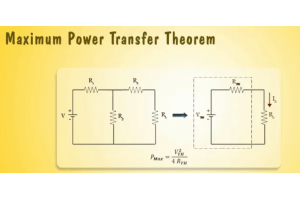

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52207