Mastering af SR -låse: Symboler, funktioner og praktiske applikationer

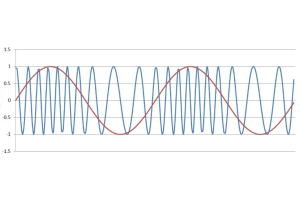

En SR -lås er et asynkron kredsløb, der fungerer uafhængigt af ursignaler, hvilket gør det til et alsidigt værktøj i forskellige applikationer.Den opretholder en binær tilstand - enten høj (1) eller lav (0) - og kan gemme en enkelt bit information, som den indeholder, indtil nye indgangssignaler dikterer en ændring.Dette grundlæggende binære lagerelement er konstrueret ved hjælp af to tværbundne logiske porte, typisk eller NAND-porte.De indstillede input (er) aktiverer låsen ved at indstille output (Q) til høj, mens nulstillingsindgangen (R) indstiller output til lavt.Imidlertid skal samtidige høje signaler på begge input fører til en udefineret tilstand, en tilstandsdesignere skal undgå.SR -låse er ikke kun teoretiske konstruktioner;De implementeres i praktiske systemer til at indeholde midlertidige data, understøtte mellemliggende behandlingsresultater og endda styre fejldetektion i kritiske applikationer såsom rumfart og medicinsk udstyr, der viser deres uundværlighed i digitalt kredsløbsdesign.Katalog

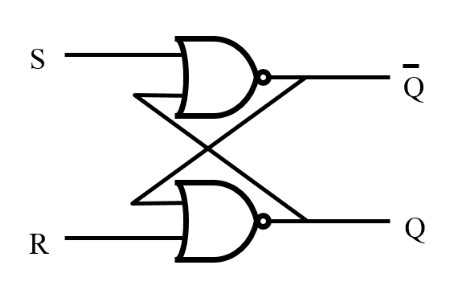

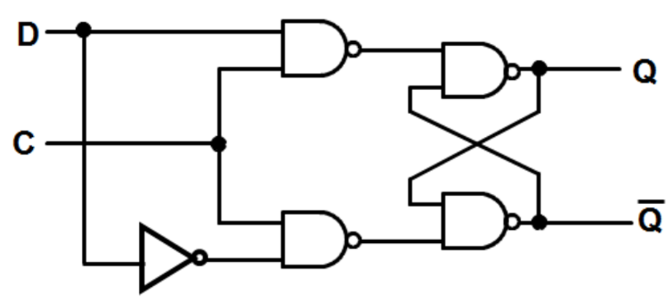

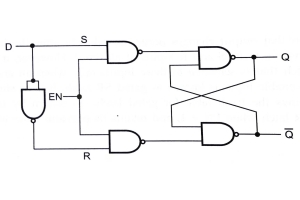

Figur 1: SR Latch

Hvad er en SR -lås?

En SR-lås eller sæt-reset-låse er et grundlæggende binært lagerelement, der hører til kategorien asynkrone kredsløb.I modsætning til synkrone kredsløb fungerer SR -låse uden et ursignal og kun er afhængig af direkte kontrol af indgangssignaler.Dette giver dem mulighed for at fungere uafhængigt inden for digitale kredsløb.En SR -lås kan opretholde to stabile tilstande: høj (1) og lav (0), hvilket gør det muligt for den at gemme en enkelt bit information, indtil de er opdateret af nye indgangssignaler.

Konstruktion af en SR-lås involverer typisk to tværbundne logiske porte, ofte eller porte eller NAND-porte.I et SR -låsedesign ved hjælp af Nor Gates er output fra hver port tilsluttet indgangen til den anden og danner en feedback -loop.Denne konfiguration sikrer, at låsen hurtigt kan ændre tilstande baseret på indgangssignalerne, mens den opretholder stabilitet, indtil en ny input beder om en ændring.

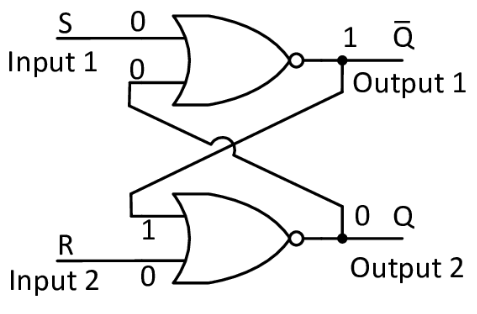

Figur 2: SR Latch (2)

Sæt input (er): Når de indstillede input (er) er aktiveret (høj), skifter låseudgangen (Q) til høj (1).

Nulstil input (R): Når nulstillingsindgangen (R) aktiveres (høj), skifter output (Q) til lav (0).

Begge input høje: Hvis både S- og R -indgange er høje samtidigt, går låsen ind i en udefineret tilstand, som bør undgås i design.

SR -låse er vigtige for midlertidig datalagring og mellemliggende resultat, der holder i digitale systemer.De er de grundlæggende elementer i mere komplekse sekventielle kredsløb som multi-bit skiftregistre, hukommelsesenheder og visse typer tællere.

I disse applikationer tilvejebringer SR -låse stabile dataopbevaring og kan hurtigt reagere på ændringer i eksterne signaler, hvilket sikrer effektiv drift af hele det elektroniske system.

En anden kritisk anvendelse af SR -låse er i fejldetektion og korrektionslogik inden for digitale kredsløb.På grund af deres evne til at holde en stabil tilstand kan de overvåge systemstatusændringer og hurtigt vende tilbage til en foruddefineret sikker tilstand ved at opdage en anomali.Denne funktion er især værdifuld i systemer med høj pålidelighed såsom rumfart og medicinsk udstyr.

Symbol på SR -låsen

At forstå dets symbol og struktur er grundlæggende for at gribe dens drift og praktisk brug.I kredsløbsdiagrammer har SR -låsen typisk to hovedindgangsporte mærket S (sæt) og R (nulstilling).Disse input kontrollerer låsens outputtilstand, ofte repræsenteret som Q. Nogle designs har også den inverse output, mærket Q ', som giver den modsatte tilstand af Q.

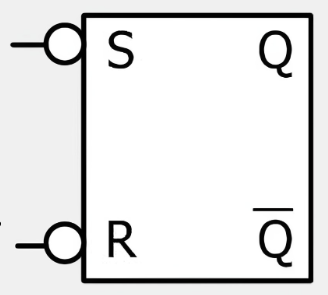

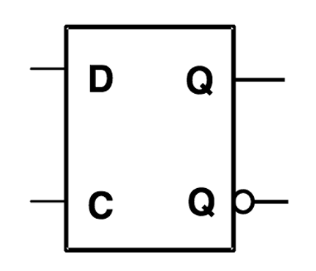

Figur 3: Symbol på SR -låsen

En SR -lås er ofte repræsenteret af et rektangulært symbol med input S og R og en output Q. I nogle tilfælde vises output Q 'også.Denne klare mærkning giver kredsløbsdesignere mulighed for hurtigt at identificere komponentens funktion og dens rolle inden for det større kredsløb.

En fælles variant af SR -låsen inkluderer et ur (CLK) input.CLK -input sikrer, at tilstandsændringer forekommer synkroniseret med ursignalet, hvilket muliggør præcis timingkontrol.I denne opsætning, selv hvis S eller R er aktiveret, opdateres Latch's tilstand kun, når CLK -signalet opfylder specifikke betingelser, normalt på stigende eller faldende kant.Dette forhindrer fejl forårsaget af indgangssignalfejl eller utilsigtede ændringer.

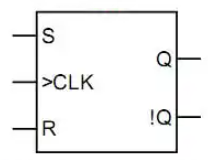

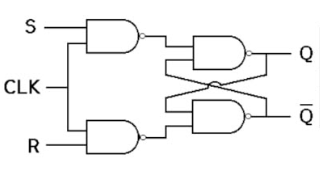

Figur 4: Symbol på det ur-gatede SR-lås

Det klokede SR -låsesymbol inkluderer S-, R- og CLK -indgange inde i et rektangel.Denne standardiserede repræsentation hjælper designere med at forstå låsens funktionalitet og dens timingkrav.F.eks. Sikrer omhyggelig CLK-kontrol i højtydende computing eller komplekse dataoverførselssystemer, der sikres og overføres nøjagtigt på hvert behandlingstrin, der optimerer den samlede systemydelse og pålidelighed.

Præcis kontrol af SR-låseindgange er vigtig, især ved design af højhastigheds- og storkapacitetshukommelse eller midlertidige datatuffere.Ved at designe logiske kredsløb til håndtering af S- og R -aktivering kan komplekse funktioner såsom databelastning, clearing eller nulstilling af tilstand opnås.Præcis CLK -signalstyring sikrer, at alle dataoperationer følger en foruddefineret timing -sekvens, hvilket markant forbedrer systemeffektiviteten og databehandlingsevnen.

En dyb forståelse af SR -latchens symbol og struktur hjælper ikke kun med korrekt kredsløbsdesign og fejlfinding, men også til at udføre komplekse digitale logiske operationer og forbedre systemets ydelse.Dette er især kritisk i applikationer, der kræver høj pålidelighed og præcis kontrol, såsom rumfart og medicinsk udstyr.

Typer af låse og deres arbejdsprincipper

Linches er grundlæggende komponenter i elektronisk design og tilbyder forskellige funktioner og brede anvendelser.De vigtigste typer låse er SR -låse og d -låse, hver med unikke operationer og brugssager.

Sr Latch

SR-låsen eller sæt-reset-låsen er en grundlæggende lagringsenhed, der kontrolleres af dens to input, S (sæt) og R (nulstilling).

Når S -input modtager et højt signal, bliver output Q høj, hvilket indikerer, at dataene er indstillet.Når R -input modtager et højt signal, bliver output Q lavt, hvilket indikerer, at dataene nulstilles.Hvis både S- og R -indgange er høje samtidig, går låsen ind i en udefineret tilstand, hvilket forårsager potentiel output -ustabilitet.Denne tilstand skal undgås i design.SR Latch's direkte respons på indgangssignaler gør det nyttigt i situationer, der kræver hurtig reaktion.

D Latch

D Latch, også kendt som en datalås eller gennemsigtig lås, tilbyder mere kompleks kontrol med dataindgang D og Clock Signal CLK.

Figur 5: D Latch

Figur 6: D Latch Symbol

Når CLK er høj, følger output Q input D, hvilket giver data mulighed for at passere gennem låsen frit.Når CLK går lavt, er den aktuelle værdi af D låst, og output Q forbliver konstant indtil det næste CLK -høje signal.Denne mekanisme gør D Latch ideel til midlertidigt lagring af data for at synkronisere forskellige behandlingshastigheder i et system.

SR- og D -låse har en uovertruffen rolle i datalagring og statsmaskinlogik.På grund af deres direkte inputniveau -respons er låse vigtige for at designe asynkrone kredsløb.De leverer vigtige funktioner til komplekse dataoverførsler og strømstyringssystemer, der effektivt lagrer statsoplysninger for at sikre stabil drift.Korrekt brug af disse låse kan forbedre kredsløbets pålidelighed og effektivitet markant, hvilket gør dem uundværlige i moderne elektroniske systemer.

Sandhedstabel for en SR -lås

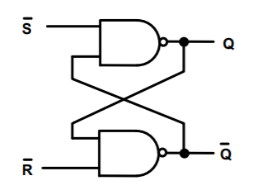

Figur 7: Sr Nand Latch

|

S |

R |

Q |

Q ' |

Bemærk |

|

0 |

0 |

1 |

1 |

FORBUDT |

|

0 |

1 |

1 |

0 |

SÆT |

|

1 |

0 |

0 |

1 |

NULSTIL |

|

1 |

1 |

Q |

Q ' |

BEHOLDE |

Diagram 1: Sandhedstabel for SR -lås ved hjælp af Nand Gates

Figur 8: Sr eller lås

|

S |

R |

Q |

Q ' |

Bemærk |

|

0 |

0 |

Q |

Q ' |

BEHOLDE |

|

0 |

1 |

1 |

0 |

NULSTIL |

|

1 |

0 |

0 |

1 |

SÆT |

|

1 |

1 |

0 |

0 |

FORBUDT |

Diagram 2: Sandhedstabel for SR Latch ved hjælp af Nor Gates

Nu tager vi sandhedstabellen i SR -låsen ved hjælp af Nor Gate som et eksempel for at forstå betydningen af sandhedstabellen i SR -låsen.

Input- og output -tilstande

Både S og R er 0: låsen forbliver i sin nuværende tilstand.Output Q forbliver den samme, hvad enten det er 0 eller 1.

S er 0 og R er 1: Låsen nulstilles, hvilket tvinger output q til 0.

S er 1 og R er 0: låsen sætter, hvilket gør output Q lig med 1.

Både S og R er 1: Denne tilstand er ugyldig eller udefineret, ofte omtalt som den "forbudte" tilstand i en SR -lås.I dette tilfælde q og q 'begge lige 0, hvilket fører til en tvetydig output.

Når S og R begge er 0, gør låsen intet og har simpelthen sin aktuelle værdi.Dette er nyttigt til at opretholde staten uden ændringer.

Når S er 0 og R er 1, fortælles låsen eksplicit at nulstille, og sørg for, at Q er 0 uanset dens tidligere tilstand.Dette er en ligetil måde at rydde låsen på.

Når S er 1 og R er 0, er låsen indstillet, hvilket sikrer, at Q bliver 1. Sådan opbevarer du en '1' i låsen.

Når S og R begge er 1, er staten ikke tilladt, fordi den får begge udgange til at være 0, hvilket er modstridende og upålideligt.Designere skal undgå denne betingelse for at sikre stabil drift.

Fordele og ulemper ved låse

Linches er vidt brugt i digitalt kredsløbsdesign på grund af deres enkelhed og lave omkostninger.Disse egenskaber gør det muligt for låse at fungere i høje hastigheder med lavt strømforbrug, hvilket gør dem ideelle til højhastigheds digitale systemer.For eksempel i processorregisterfiler kan låse hurtigt gemme og hente data, hvilket øger behandlingshastigheden og effektiviteten markant.

Fordele ved låse

Enkelhed og omkostningseffektivitet: låse er ligetil komponenter, der er billige at implementere i digitale kredsløb.

Høj hastighed og lav effekt: Deres design giver mulighed for hurtig drift med minimalt strømforbrug, hvilket er kritisk i højhastigheds digitale systemer.

Effektivitet i datahåndtering: I applikationer som processorregisterfiler leverer låse hurtige datalagring og hentning, hvilket forbedrer den samlede systemydelse.

Ulemper ved låse

På trods af deres fordele har låse bemærkelsesværdige begrænsninger i visse design og applikationer.

Uforudsigelig opførsel i asynkrone design: Uden klokkekontrol kan låse opføre sig uforudsigeligt.I SR -låse, hvis begge indstillinger (r) og nulstilling (R) -indgange er høje samtidigt, bliver output udefineret, hvilket fører til ustabilitet.Dette er problematisk i realtidskontrol eller sikkerhedskritiske anvendelser, hvor pålidelig output er afgørende.

Kompleks timingdesign: Design med låse kræver omhyggelig timingovervejelser.Ingeniører skal redegøre for forsinkelser i signalformering og raceforhold for at undgå timingfejl.Forkert design kan resultere i dataændringer, før ursignalet stabiliseres, hvilket forårsager datakorruption eller forkert datafangst.Dette kræver en dyb forståelse af timinganalyse og kredsløbsadfærd.

For at tackle disse udfordringer kan der anvendes specifikke designteknikker og strategier:

Synkroniseringsmekanismer: Tilføjelse af synkroniseringsmekanismer kan hjælpe med at håndtere asynkrone input og afbøde uforudsigelig opførsel.

Brugerdefineret urstyring: Implementering af tilpassede urstyringsstrategier kan sikre, at data låses korrekt og til de rigtige tidspunkter.

Brug af EDA -værktøjer: Moderne elektronisk designautomation (EDA) -værktøjer tilbyder avancerede analyse- og optimeringsfunktioner.Disse værktøjer hjælper med at forudsige og løse timing og synkroniseringsproblemer i designfasen, hvilket forbedrer pålideligheden og ydelsen af digitale systemer ved hjælp af låse.De hjælper designere med at identificere potentielle problemer tidligt, hvilket sikrer, at det endelige produkt fungerer pålideligt under forskellige forhold.

Praktiske anvendelser af SR -låse

SR -låse, der er kendt for deres evne til hurtigt og pålideligt at opretholde tilstand, er vidt brugt i forskellige elektroniske systemer.De udmærker sig i scenarier, der kræver midlertidig datalagring eller statsopbevaring.

Midlertidig datalagring

SR -låse bruges ofte i cachehukommelse til midlertidigt at gemme data.Dette giver systemet mulighed for hurtigt at få adgang til ofte anvendte data, hvilket øger databehandlingsfunktionerne og effektiviteten af store processorer markant.

Lagringsregisterfiler

I processorer muliggør SR -låse hurtig opbevaring og hentning af data i registerfiler, forbedring af behandlingshastigheden og den samlede systemydelse.

Vedligeholdelse af kontrolsignaler

I digitale kontrolsystemer er SR -låse nyttige til at opretholde tilstanden for visse kontrolsignaler, indtil eksterne betingelser eller systemlogik dikterer en ændring.De hjælper også med at bevare stater inden for systemet og sikrer ensartet ydelse i operationer, der kræver præcision og pålidelighed.

Trigger og tæller kredsløb

SR-låsebaserede flip-flops bruges ofte i kredsløb, der kræver synkroniseret operation, såsom digitale ure og timere.De kontrollerer tællerimpulser, hvilket sikrer nøjagtig tidtager og pålidelig ydelse.Disse kredsløb er afhængige af SR -låse for at opretholde nøjagtige tællinger, hvilket letter timing og sekventering i digitale systemer.

Mekaniske interaktioner

SR -låse er effektive til at eliminere mekanisk afvisning i afbrydere.En mekanisk afvisning opstår, når en switch genererer hurtige, gentagne signalændringer på grund af dårlig kontakt.SR -låse stabiliserer udgangssignalet og forhindrer fejl forårsaget af støjende signaler.

SR-flip-flop

En SR-flip-flop, ofte kaldet en kant-udløst sæt-reset-flip-flop, består af to sammenkoblede SR-låse.Denne dobbelt-latch-struktur gør det muligt for den at reagere på specifikke ursignalkanter (enten stigende eller falde) for at ændre sin tilstand.Dette opnås gennem speciel logisk kontrol mellem låsene.Outputet fra den første lås bliver en del af input til den anden lås, og output fra den anden lås påvirker til gengæld den første lås, hvilket skaber en sammenlåsende feedback -loop.

Figur 7: SR-flip-flop

SR-flip-flop ændrer tilstand nøjagtigt ved urets signalets stigende eller faldende kant.Den sammenlåsende feedback mellem de to SR-låse sikrer, at flip-flop kun ændrer tilstand som respons på urkanten, hvilket giver stabil og pålidelig output.

I mikroprocessorer og digitale signalprocessorer bruges SR-flip-flops til prøveudtagning og opbevaring af data.De fanger og stabiliserer data ved specificerede urkanter, hvilket sikrer pålidelig efterfølgende databehandling og analyse.

Den kant-triggerende mekanisme hjælper med at undgå raceforhold, hvor forskellige dele af kredsløbet kan ændre tilstand på samme tid uden synkronisering, hvilket potentielt resulterer i ustabile eller forkerte output.SR-flip-flops er afgørende for implementering af specifik kommunikationsprotokollogik, såsom rammesynkronisering og fejldetektion.Deres stabilitet og hurtige responstid hjælper med at bevare datatransmissionskvalitet og system pålidelighed.

Forbidde stater i SR-låse og SR-flip-flops

Når vi designer SR-låse og SR-flip-flops ved hjælp af NAND og NOR-porte, er vi alle nødt til at være opmærksomme på at styre og undgå hæmmede tilstande.En forbudt tilstand opstår, når både sæt (er) og nulstilling (R) input er samtidig høje (for NAND -porte) eller lave (for NOR -porte).Denne kombination fører til en ubestemt outputtilstand, da output afhænger af den forrige tilstand af kredsløbet, hvilket gør den uforudsigelig.

Forbidden stater i Nand Gate SR Latches

Når både S og R er lave, går begge udgange højt, hvilket krænker låsens komplementære outputkarakteristik.Dette resulterer i en ubestemt tilstand.

Forbidden stater i Nor Gate SR Latches

Når både S og R er høje, går begge udgange lave, hvilket også skaber en ubestemt tilstand.Dette kan føre til uforudsigelig opførsel i kredsløbet.

Praktiske tilgange for at undgå forbudte stater

Tilføjelse af kontrollogik

Brug yderligere logiske porte til at overvåge staterne S og R. Hvis begge input -tendens til en forbudt tilstand, skal du automatisk justere et input for at forhindre den ubestemte tilstand.Dette sikrer, at outputene forbliver stabile og forudsigelige.Implementere en logisk port, der griber ind, når S og R begge er høje (eller lave), og justerer et input for at opretholde en gyldig tilstand.

Softwaresimulering og hardware -test

Foretag grundige softwaresimuleringer for at identificere potentielle forbudte tilstande under forskellige driftsbetingelser.Dette giver designere mulighed for at se og rette logiske fejl inden fysisk implementering.Udfør omfattende hardwaretest for at validere, at kredsløbet håndterer alle inputkombinationer korrekt.Dette trin hjælper med at sikre, at låsen eller flip-flop fungerer pålideligt i scenarier i den virkelige verden.

Konklusion

Alsidigheden og pålideligheden af SR Latches understreger deres betydning i digitalt kredsløbsdesign.Ved at udforske den nuancerede opførsel af SR -lås gennem deres symbolrepræsentationer, sandhedstabeller og praktiske anvendelser får vi en omfattende forståelse af deres drift og betydning.På trods af de potentielle faldgruber i udefinerede tilstande i asynkrone design, kan strategisk implementering af kontrollogik og omfattende simulering afbøde disse risici.Advanced Electronic Design Automation (EDA) -værktøjer forbedrer pålideligheden og ydelsen af kredsløb, der indeholder SR -låse ved at forudsige og løse timing og synkroniseringsproblemer.Uanset om det bruges i midlertidig datalagring, kontrol af signalvedligeholdelse eller fejldetektion, viser SR -låse at være grundlæggende i at skabe robuste og effektive digitale systemer.Deres rolle i højhastighedshukommelsesoperationer og synkron databehandling i komplekse applikationer eksemplificerer deres vedvarende relevans.Efterhånden som teknologien skrider frem, fortsætter de principper, der styrer SR -låse, og inspirerer innovationer inden for digital elektronik, hvilket sikrer, at disse elementære komponenter forbliver integrerede i udviklingen af sofistikerede og pålidelige elektroniske enheder.

Ofte stillede spørgsmål [FAQ]

1. Hvad er en SR -lås?

En SR-lås eller sæt-reset-låse er et grundlæggende binært lagerelement, der bruges i digitale kredsløb.Det er et asynkron kredsløb, hvilket betyder, at det fungerer uden et ursignal, der er afhængig af direkte kontrol af dets input til ændringstilstande.

2. Hvad er SR's funktion i logik?

I logik kontrollerer SR (Set-Reset) -indgangene staten for låsen.

3. Hvilken type logikport bruger en SR -lås?

En SR -lås bruger typisk enten eller porte eller NAND -porte.I en NOR-portbaseret SR-lås føres output fra hver Nor Gate tilbage til indgangen til den anden, hvilket skaber en stabil feedback-loop.I en NAND-portbaseret SR-lås bruges en lignende feedbackkonfiguration, men de logiske niveauer er omvendt sammenlignet med den NOR-portbaserede lås.Begge konfigurationer opnår den samme grundlæggende funktionalitet som vedligeholdelse af en binær tilstand baseret på sæt- og nulstillingsindgange.

4. Hvordan fungerer en lås?

En lås fungerer ved at bruge feedback til at opretholde sin outputtilstand baseret på de leverede input.I en SR -lås kontrollerer sæt (er) og nulstilling (R) -indgange tilstanden for output (Q).Når det indstillede input er aktiveret (højt), indstilles output til høj (1).Når nulstillingsindgangen aktiveres (høj), nulstilles output til lav (0).Feedback -loopen i låsens design sikrer, at når en outputtilstand er etableret, forbliver den stabil, indtil et nyt indgangssignal ændrer det.

5. Hvad er ulempen med en SR -lås?

Den primære ulempe ved en SR -lås er den udefinerede tilstand, der opstår, når begge indstillinger (r) og nulstilling (R) -indgange er høje samtidigt.Denne tilstand fører til en ubestemt outputtilstand, som kan forårsage ustabilitet og uforudsigelig opførsel i digitale kredsløb.Denne "forbudte" tilstand skal undgås i design for at sikre pålidelig drift.

SR Latch, Set-Reset Latch, Asynchronous Circuit, Binary Storage Element, Digital Circuits eller Gates, Nand Gates, Feedback Loop, High State, Low State, Udefineret tilstand, ursignal, direkte kontrol, midlertidig datalagring, mellemliggende resultatholdning,Fejldetektion, rumfartsapplikationer, medicinsk udstyr, kredsløbsdesign, uret SR-lås, indgangssignaler, symbol og struktur, hukommelse med høj hastighed, databuffere, timingkontrol, præcis kontrol, tilstandsopbevaring, mikroprocessorer, digitale signalprocessorer, dataprøvetagning, dataOpbevaring, kant-udløst, SR-flip-flop, sammenlåsende feedback, raceforhold, kommunikationsprotokollogik, rammesynkronisering, fejldetektion, signalfejl, elektronisk designautomation, EDA-værktøjer, synkroniseringsmekanismer, brugerdefineret urstyring, timingfejl, propagationsaddelinger, DEPAYS,Raceforhold, komplekse dataoverførsler, strømstyringssystemer, mekanisk afvisning, praktiske applikationer, digitale kontrolsystemer, logiske porte, softwaresimuleringer, hardwaretest, forbudte tilstande, låsepålidelighed.

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

En guide til det grundlæggende i D flip -flops - kredsløb, sandhedstabeller, typer, fordele og begrænsninger

på 2024-05-17

Sammenlignende guide til analyse af rheostat og potentiometre

på 2024-05-17

Populære indlæg

-

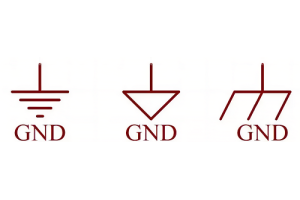

Hvad er GND i kredsløbet?

på 1970-01-01 3274

-

RJ-45 Connector Guide: RJ-45 Stikfarvekoder, ledningsordninger, R-J45-applikationer, RJ-45 datablad

på 1970-01-01 2817

-

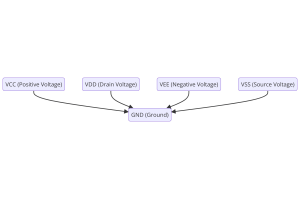

Forståelse af strømforsyningsspændinger i elektronik VCC, VDD, VEE, VSS og GND

på 0400-11-20 2645

-

Fiberstikstyper: SC vs LC og LC vs MTP

på 1970-01-01 2266

-

Sammenligning mellem DB9 og RS232

på 1970-01-01 1882

-

Hvad er et LR44 -batteri?

Elektricitet, den allestedsnærværende kraft, roligt gennemsyrer alle aspekter af vores daglige liv, fra trivielle gadgets til livstruende medicinsk udstyr, det spiller en stille rolle.Imidlertid er det ingen let opgave at gribe ind i denne energi, især hvordan man opbevarer og effektivt udsender den.Det er på denne baggrund, at denne artikel vil fokusere på en type møntcellebatteri, der kan ...på 1970-01-01 1846

-

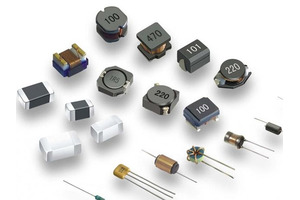

Forståelse af de grundlæggende elementer: induktansresistens, og kapacitet

I den komplicerede dans inden for elektroteknik tager en trio af grundlæggende elementer centrum: induktans, modstand og kapacitans.Hver bærer unikke træk, der dikterer de dynamiske rytmer af elektroniske kredsløb.Her går vi på en rejse for at dechiffrere kompleksiteten af disse komponenter for at afsløre deres forskellige roller og praktiske anvendelser inden for det store elektriske o...på 1970-01-01 1809

-

Hvad er RF, og hvorfor bruger vi det?

Radiofrekvens (RF) -teknologi er en vigtig del af moderne trådløs kommunikation, der muliggør datatransmission over lange afstande uden fysiske forbindelser.Denne artikel dækker det grundlæggende i RF og forklarer, hvordan elektromagnetisk stråling (EMR) gør RF -kommunikation mulig.Vi vil udforske principperne for EMR, oprettelse og kontrol af RF-signaler og deres omfattende anvendelser.Art...på 1970-01-01 1801

-

CR2430 Batteri Comprehensive Guide: Specifikationer, applikationer og sammenligning med CR2032 -batterier

Hvad er CR2430 -batteri?Fordele ved CR2430 -batterierNormCR2430 Batteri applikationerCR2430 ækvivalentCR2430 vs CR2032Batteri CR2430 størrelseHvad man skal kigge efter, når man køber CR2430 og ækvivalenterDatablad PDFOfte stillede spørgsmål Batterier er hjertet i små elektroniske enheder.Blandt de mange tilgængelige typer spiller møntceller en afgørende rolle, der ofte findes i regnemas...på 1970-01-01 1800

-

Omfattende guide til HFE i transistorer

Transistorer er afgørende komponenter i moderne elektroniske enheder, hvilket muliggør signalforstærkning og kontrol.Denne artikel dækker i viden omkring HFE, herunder hvordan man vælger en transistors HFE -værdi, hvordan man finder HFE og gevinsten af forskellige typer transistorer.Gennem vores udforskning af HFE får vi en dybere forståelse af, hvordan transistorer fungerer og deres rolle...på 5600-11-20 1782