EP2S60F672C4 FPGA: Funktioner, applikationer, programmering og databladsvejledning

I denne vejledning får du en klar oversigt over EP2S60F672C4, en stærk FPGA fra Intels Stratix II -familie.Du lærer om dets vigtigste funktioner, arkitektur, blokstruktur og tekniske specifikationer for at forstå, hvordan det passer ind i avancerede digitale design.Det leder dig også gennem dens programmeringstrin, applikationer, fordele og ulemper, så du kan se nøjagtigt, hvor og hvordan denne enhed kan bruges.Katalog

Hvad er EP2S60F672C4?

De EP2S60F672C4 er en FPGA med høj densitet fra Intel (tidligere Altera), der hører til Stratix II-familien.Den er bygget på en 90 nm, 1,2 V kobber SRAM-proces, og den leverer betydelig logisk kapacitet inden for en 672-ball FBGA-pakke, hvilket gør den ideel til komplekse digitale systemer.Som en del af EP2S-serien sidder “60” -enheden i midten til øvre rækkevidden af Stratix II-opstillingen og tilbyder en stærk balance mellem logikdensitet, indlejret hukommelse og I/O-ressourcer.Denne FPGA er kendt for sin robuste arkitektur og pålidelighed og forbliver et betroet valg i mange avancerede designs.

Leder du efter EP2S60F672C4?Kontakt os for at kontrollere den aktuelle lager, ledetid og prisfastsættelse.

EP2S60F672C4 CAD -modeller

EP2S60F672C4 Symbol

EP2S60F672C4 Fodaftryk

EP2S60F672C4 3D -model

EP2S60F672C4 -funktioner

• Avanceret 90 nm, 1,2 V CMOS -proces

EP2S60F672C4 er fremstillet på en 90 nm allayer kobber CMOS-proces, der kører med en 1,2 V kernespænding.Denne teknologi muliggør høj hastighed, reduceret strømforbrug og større logikdensitet sammenlignet med ældre FPGA -generationer.

• Adaptiv Logic Module (ALM) Arkitektur

Enheden bruger almisser som dens logiske byggesten i stedet for traditionelle logiske elementer.Denne arkitektur forbedrer ressourceudnyttelsen, hvilket gør det muligt at implementere mere komplekse logiske funktioner effektivt inden for det samme siliciumområde.

• Høj logikdensitet

Med cirka 60.440 logiske elementer (24.176 almisser) understøtter FPGA store og sofistikerede digitale design.Denne høje kapacitet gør det velegnet til applikationer såsom signalbehandling, kommunikation og indlejrede kontrolsystemer.

• Trimatrix ™ on-chip hukommelse

EP2S60F672C4 integrerer tre typer RAM-blokke (M512, M4K og M-RAM) for at tilvejebringe i alt ca. 2,4 MBITs indlejret hukommelse.Denne blanding giver mulighed for at implementere små Fifos, mellemstore buffere og store dobbeltporthukommelser effektivt.

• Dedikerede DSP -blokke

Enheden inkluderer 36 dedikerede DSP -blokke designet til aritmetiske operationer som multiplikationer, akkumuleringer og FIR -filtrering.Disse blokke øger ydelsen i beregningsintensive opgaver, mens de gemmer generelle logiske ressourcer.

• Højhastigheds I/O og signalintegritet

Det understøtter forskellige enkelt-endelige I/O-standarder sammen med dynamisk fasejustering (DPA) kredsløb.Disse funktioner muliggør stabile dataoverførsel med høj hastighed op til 1 Gbps, hvilket sikrer pålidelig kommunikation med eksterne komponenter.

• Rich ekstern hukommelsesgrænseflade support

FPGA er kompatibel med DDR, DDR2, QDR II, RLDRAM II og andre hukommelsesstandarder.Indbygget interface support forenkler bestyrelsesdesign og opnår høj data gennemstrømning til hukommelsesintensive applikationer.

• Fleksibel urstyring

Op til 12 On-Chip PLL'er tillader multiplikation af ur, opdeling, faseforskydning og fejlfri overgang.Du kan finjustere ur-domæner og reducere jitter, der understøtter interne urfrekvenser på op til 500–550 MHz.

• Bitstream -kryptering og rekonfiguration

EP2S60F672C4 understøtter AES-baserede Bitstream-kryptering for at sikre intellektuel ejendom.Det tilbyder også ekstern rekonfigurationsevne, der muliggør opdateringer i feltet uden at udskifte enheden.

Stratix II -blokdiagram

Stratix II -blokdiagrammet, som vist for EP2S60F672C4, illustrerer det interne arrangement af logik, hukommelse og DSP -ressourcer, der danner FPGA's kerne.Logikarrayblokke (laboratorier) er arrangeret i et almindeligt gitter, omgivet af indlejrede RAM- og DSP-søjler, der giver hurtig aritmetik og on-chip lagerkapaciteter.Perifere I/O -elementer og urnetværk indrammer denne struktur, hvilket muliggør effektiv dataoverførsel og timingkontrol mellem FPGA og eksterne enheder.Dette diagram er vigtigt, fordi det hjælper med at forstå, hvordan forskellige funktionelle blokke er fysisk organiseret, så de kan optimere placering, routing og den samlede systemydelse.

Stratix II I/O Banks Diagram

Denne Stratix II I/O Banks -diagram illustrerer, hvordan input/output -stifterne af EP2S60F672C4 er grupperet, og hvilke elektriske standarder hver gruppe understøtter.Hver I/O -bank er designet til at håndtere specifikke spændingsniveauer, signaltyper og funktioner såsom LVTTL, SSTL, LVD'er eller urindgangsstandarder.Layoutet viser, hvordan forskellige banker (f.eks. 1, 2, 5, 6 vs. 3, 4, 7, 8 osv.) Optimeres til enten generel I/O eller højhastighedsdifferential signalering, herunder understøttelse af LVDS/LVPECL-urindgange ved kanterne.At forstå denne struktur er vigtig, når man tildeler stifter, fordi korrekt bankudvælgelse sikrer elektrisk kompatibilitet, forenkler bestyrelsesruting og maksimerer FPGAs ydeevne i højhastighedsdesign.

EP2S60F672C4 -specifikationer

|

Type |

Parameter |

|

Fabrikant |

Altera/Intel |

|

Serie |

Stratix® II |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Antal laboratorier/CLB'er |

3022 |

|

Antal logiske elementer/celler |

60.440 |

|

Samlede rambits |

2.544.192 |

|

Antal I/O. |

492 |

|

Spænding - Forsyning |

1,15 V ~ 1,25 V |

|

Monteringstype |

Overflademontering |

|

Driftstemperatur |

0 ° C ~ 85 ° C (TJ) |

|

Pakke / sag |

672-BBGA |

|

Leverandørenhedspakke |

672-fbga (27 × 27) |

|

Basisproduktnummer |

EP2S60 |

EP2S60F672C4 -applikationer

1. Digital signalbehandling (DSP) og filtrering

EP2S60F672C4 er velegnet til implementering af højtydende DSP-funktioner såsom FIR- og IIR-filtre, FFT-behandling og komplekse aritmetiske operationer.Dens dedikerede DSP -blokke håndterer multiplikationer og akkumuleringer effektivt, hvilket frigør generelle logiske ressourcer til andre opgaver.On-Chip Trimatrix ™ -hukommelsen muliggør glat databuffering og rørledning, hvilket er fantastisk til realtidsbehandling med høje prøvepriser.Dette gør enheden ideel til avanceret lyd-, video- og radarsignalapplikationer.

2. Højhastighedskommunikation og netværk

FPGAs højhastigheds I/O-grænseflader og dynamiske fasejustering (DPA) kredsløb support pålidelig, gigabit-niveau datatransmission.Det kan implementere kommunikationsprotokoller og fysiske lagfunktioner for systemer som routere, switches og backplan -forbindelser.Med sin store logiske kapacitet og fleksible PLL'er kan den håndtere komplekse timing og protokolkonverteringer mellem flere højhastighedsgrænseflader.Disse muligheder gør det til en stærk pasform til telekominfrastruktur og netværksudstyr med høj båndbredde.

3. hukommelseskontrollere og databehandlingssystemer

EP2S60F672C4 understøtter forskellige eksterne hukommelsesgrænseflader, herunder DDR, DDR2, RLDRAM II og QDR II, hvilket gør det ideelt til at designe hukommelsescontrollere med høj båndbredde.Det kan håndtere databuffering, adressegenerering og voldgift ved høje hastigheder med minimal latenstid.Kombinationen af hurtige urnetværk og indlejrede RAM -blokke tillader effektiv styring af store datastrømme.Dette gør FPGA velegnet til billedbehandling, videostreaming og videnskabelige beregningsplatforme, der er afhængige af tunge data gennemstrømning.

4. brugerdefineret logik og indlejret acceleration

Med over 60.000 logiske elementer og rig urstyring kan FPGA være vært for tilpassede hardwareacceleratorer til specifikke algoritmer.Designere bruger det ofte til at aflaste beregningsmæssigt intensive opgaver fra CPU'er, såsom kryptering, protokolparsing eller realtidskontrolsløjfer.Det kan også integrere flere funktionelle blokke, hvilket gør det velegnet til komplekse SOC-lignende design.Denne fleksibilitet gør det værdifuldt i applikationer som industriel automatisering, sikkerhedssystemer og luftfartsstyringsenheder.

5. Prototyping og uddannelsesudviklingsplatforme

EP2S60 -enheden findes ofte på FPGA -udviklingssæt, der bruges til prototype, test og akademisk forskning.Dens balance mellem logisk kapacitet, I/O -antal og DSP -kapaciteter giver ingeniører og studerende mulighed for at implementere og verificere fulde systemer på en enkelt chip.Det understøtter hurtig iteration af digitale design, der muliggør hardware -verifikation, før de forpligter sig til ASIC -udvikling.Mange universiteter og F & U -laboratorier bruger det til at undervise i avanceret digital design- og signalbehandlingskoncepter.

EP2S60F672C4 lignende dele

|

Specifikation |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Familie / serie |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Logiske elementer (LE) |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

|

Alms |

24.176 |

24.176 |

24.176 |

24.176 |

24.176 |

24.176 |

|

Pakke |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Hastighedskvalitet |

C4 (STD) |

C3 (hurtigere) |

C5 (hurtigere) |

C5 (hurtigere) |

I4 (std) |

I3 (hurtigere) |

|

Temperaturklasse |

Kommerciel (0 ~ 70 ° C) |

Kommerciel |

Kommerciel |

Kommerciel |

Industriel (−40 ~ 100 ° C) |

Industriel (−40 ~ 100 ° C) |

|

I/O -stifter |

492 |

492 |

492 |

492 |

492 |

492 |

|

On-chip hukommelse |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

|

Kerne spænding |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

|

Nøgleforskel |

Baseline kommerciel hastighed |

C3 Speed Bin, Lead-Free “N” |

Højere hastighedsbakke |

Højere hastighedsbakke, “N” -variant |

Industriel temperatur, samme densitet |

Industriel, hurtigere hastighed, blyfri |

EP2S60F672C4 -programmeringstrin

Inden du kan bruge EP2S60F672C4 FPGA i dit design, skal du konfigurere det korrekt med dine kompilerede bitstream.Denne proces involverer at forberede programmeringsfilen, indstille hardware-grænsefladen og sikre, at konfigurationen indlæses korrekt på power-up.

Trin 1: Opret og kompiler dit design

Du begynder med at udvikle dit logikdesign ved hjælp af Intel Quartus II -software.Når du er færdig med designet, kompilerer du det for at generere programmeringsfilen (.sof eller .POF) specifikt til EP2S60F672C4 -enheden.Samlingsprocessen kontrollerer for timing, pin -opgaver og ressourceforbrug for at sikre, at dit design passer inden for FPGAs arkitektur.Når den er samlet, er dine bitstream klar til enhedskonfiguration.

Trin 2: Opret programmeringshardware

Dernæst forbereder du den fysiske programmeringsgrænseflade mellem din pc og FPGA -kortet.Dette involverer typisk tilslutning af en USB-blaster eller kompatibelt JTAG-kabel til enhedens JTAG-port.Du skal kontrollere, at Quartus II genkender programmereren, og at målenheden er korrekt detekteret.Dette trin sikrer stabil kommunikation, inden konfigurationsprocessen påbegynder.

Trin 3: Indlæs programmeringsfilen i enheden

Ved hjælp af Quartus II -programmørværktøjet tilføjer du den kompilerede .sof eller .POF -fil og vælger EP2S60F672C4 fra listen over detekteret enhed.Derefter initierer du programmeringssekvensen, hvor bitstream overføres og indlæses i FPGAs SRAM -konfigurationsceller.Du skal overvåge statuslinjen og statusmeddelelser for at bekræfte en vellykket konfiguration.Når FPGA først er afsluttet, begynder FPGA med at udføre den programmerede logik med det samme.

Trin 4: Kontroller konfigurationen og operationen

Efter programmering bekræfter du, at enheden fungerer som tilsigtet.Quartus II giver en verifikationsmulighed til at kontrollere konfiguration CRC og statussignaler, hvilket sikrer, at designet indlæses korrekt.Du kan også teste dine I/O -funktioner eller køre en funktionel simulering for at bekræfte systemadfærd.Dette sidste trin sikrer, at dit design er fuldt operationelt og stabilt på hardware.

EP2S60F672C4 Fordele og ulemper

Fordele

• Høj logikdensitet for komplekse design

• Godt præstation-til-omkostningsforhold

• Nem migration inden for den samme familie

• Stabile og modne udviklingsværktøjer

• Bevist pålidelighed i industriel brug

Ulemper

• Forældet og sværere at købe

• Højere strømforbrug end nyere FPGA'er

• Ingen moderne højhastighedstransceivere

• vanskeligere tidsafslutning ved høj udnyttelse

• Begrænset skalerbarhed for fremtidige protokoller

EP2S60F672C4 Emballagedimensioner

|

Type |

Parameter |

|

Pakningstype |

672-fbga (Fineline BGA) |

|

Kropsstørrelse (L × W) |

27,00 mm × 27,00 mm |

|

Samlet pakkehøjde (a) |

Max 3,50 mm |

|

Standoffhøjde (A1) |

Min 0,30 mm |

|

Substrattykkelse (A2) |

Maks. 3,00 mm |

|

Kuglediameter (b) |

0,50 mm - 0,70 mm |

|

Ball Pitch (E) |

1,00 mm |

|

Antal bolde |

672 |

|

Monteringstil |

Overflademontering |

|

Pakkebeskrivelse |

FBGA, 27 × 27 mm gitter |

EP2S60F672C4 Producent

EP2S60F672C4 FPGA er fremstillet af Altera Corporation, en førende pioner inden for programmerbare logiske enheder.I 2015 blev Altera erhvervet af Intel, og produktet falder nu ind under Intels Programmerbare Solutions Group (PSG), der fortsætter med at støtte og levere Alteras etablerede FPGA -familier.Intel opretholder Stratix II-linjen som en del af sin ældre produktportefølje, hvilket sikrer dokumentation, værktøjsstøtte og langsigtet tilgængelighed for industrielle og kommunikationsapplikationer.

Konklusion

EP2S60F672C4 kombinerer høj logikdensitet, fleksibel hukommelsesarkitektur og robuste I/O -funktioner til at understøtte komplekse digitale systemer.Dets ALM-baserede design, Trimatrix ™ -hukommelse, DSP-blokke og urstyringsfunktioner muliggør effektiv implementering af krævende applikationer.Mens det giver bevist pålidelighed og moden udviklingsstøtte, står den over for begrænsninger som forældelse og mangel på moderne transceivere sammenlignet med nyere FPGA -generationer.Generelt gør dens afbalancerede ydelse og alsidighed det til et solidt valg til signalbehandling, kommunikation, datahåndtering og prototype applikationer.

Datablad PDF

EP2S60F672C4 Datablad:

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Kan EP2S60F672C4 arbejde med moderne DDR -hukommelsesgrænseflader?

Ja, det understøtter DDR, DDR2, QDR II og RLDRAM II -grænseflader, der dækker mange almindelige eksterne hukommelsesstandarder.Dette gør det velegnet til højbåndbredde databehandlingsapplikationer.

2. Kræver EP2S60F672C4 særlig håndtering eller opbevaring?

Ja, ligesom andre BGA-pakkede komponenter, skal den opbevares i fugtstyret emballage og håndteres med ESD-beskyttelse.Efter korrekt opbevaringspraksis hjælper med at bevare loddeligheden og enhedens pålidelighed under samlingen.

3. Hvordan kan du reducere strømforbruget i EP2S60F672C4 -design?

Du kan optimere logikudnyttelsen, port ubrugte ure, lavere I/O-spændinger, hvor det er muligt, og gearing af effektbevidst syntesemuligheder i Quartus II for at minimere den samlede effekttrækning.

4. Hvilke programmeringsværktøjer kræves til EP2S60F672C4?

Du har brug for Intel Quartus II-software til design, kompilering og programmering sammen med en USB-blaster eller kompatibelt JTAG-kabel til at konfigurere enheden.

5. Support EP2S60F672C4-opdateringer i feltopdateringer eller fjernbetjening?

Ja, det understøtter AES-baserede Bitstream-kryptering og fjernbetjening af genfinding, så du kan opdatere dit system sikkert uden fysisk at udskifte FPGA.

Alt om LFXP6C-3FN256C Gitter Semiconductor

på 2025-10-06

XC2C256-7TQ144C CPLD: pinout, funktioner, programmering og databladsvejledning

på 2025-10-03

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-19 147780

-

USB-C pinout og funktioner

på 2000-04-19 112050

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-19 111352

-

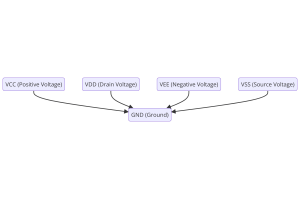

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-19 83806

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79608

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66991

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63113

-

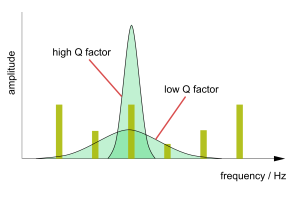

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63050

-

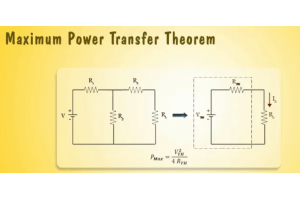

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52199