XC2C256-7TQ144C CPLD: pinout, funktioner, programmering og databladsvejledning

I denne vejledning får du et klart kig på XC2C256-7TQ144C, en CPLD med lav effekt fra Xilinx's Coolrunner-II-familie (nu AMD).Du lærer om dens PIN-konfiguration, CAD-modeller og hovedfunktioner som logisk kapacitet, I/O-indstillinger, spændingsstøtte og strømbesparende funktioner.Vi går også gennem dens arkitektur, I/V -kurve og specifikationer, efterfulgt af applikationer, lignende dele, programmeringstrin, fordele og ulemper, emballageoplysninger og producentoplysninger, så du kan forstå nøjagtigt, hvordan denne enhed passer ind i dine projekter.Katalog

Hvad er XC2C256-7TQ144C?

De XC2C256-7TQ144C er en CPLD med lav effekt (kompleks programmerbar logikenhed) fra Xilinx's Coolrunner-II-familie, nu en del af AMD.Den har 256 makroceller og kommer i en 144-polet TQFP-pakke, designet til hurtig, deterministisk drift med minimalt strømforbrug.Operation på en 1,8 V-kerne tilbyder den pålidelig ydelse i en kompakt formfaktor og er velegnet til design, der kræver øjeblikkelig kapacitet og effektiv logikimplementering.Som en del af den alsidige Coolrunner-II-serie drager den fordel af en gennemprøvet arkitektur og bred designkompatibilitet.

Leder du efter XC2C256-7TQ144C?Kontakt os for at kontrollere den aktuelle lager, ledetid og prisfastsættelse.

XC2C256-7TQ144C pin-out diagram

XC2C256-7TQ144C-pin-out-diagrammet viser, hvordan 144-stifterne er arrangeret til strøm, jord, JTAG og brugerprogrammerbare I/O-funktioner.De fleste stifter er I/O, som kan konfigureres som input eller output, og fordeles jævnt til understøttelse af fleksibel routing.VCC, VCCIO1, VCCIO2, VAUX og GND -stifter placeres omkring pakken for at tilvejebringe stabil effektfordeling og flere I/O -spændingsmuligheder.JTAG-stifterne (TDI, TDO, TMS, TCK) er grupperet sammen for let programmering og testning af systemet.

XC2C256-7TQ144C CAD-modeller

XC2C256-7TQ144C Symbol

XC2C256-7TQ144C fodaftryk

XC2C256-7TQ144C 3D-model

XC2C256-7TQ144C-funktioner

• Enhedstype og familie

XC2C256-7TQ144C er en kompleks programmerbar logikenhed (CPLD), der hører til Coolrunner-II-familien udviklet af Xilinx (nu AMD).Det er designet til lavt strømforbrug, mens den opretholder hurtig, deterministisk logisk ydelse, hvilket gør den ideel til kontrollogik og grænsefladeapplikationer.

• Logisk kapacitet

Denne enhed indeholder 256 makroceller, som er de programmerbare logiske ressourcer i CPLD.Disse makroceller kan konfigureres til at implementere forskellige kombinations- og sekventielle logikfunktioner, hvilket giver moderat kapacitet til kontrol, limlogik og busgrænseflader.

• Logikblokke (funktionsblokke)

Det integrerer 16 funktionsblokke, der organiserer og administrerer grupper af makroceller.Hver blok leverer lokale sammenkoblings- og produktfremstillingsressourcer, hvilket tillader fleksibel logikimplementering og effektiv routing inden for enheden.

• Bruger I/O -stifter

XC2C256-7TQ144C tilbyder op til 118 bruger-konfigurerbare I/O-stifter i sin TQFP-144-pakke.Denne høje pin-tælling gør det muligt for enheden at interface med flere delsystemer samtidigt, hvilket gør den egnet til komplekse bordniveau-design.

• Core Voltage (VCC)

Kernen fungerer på en nominel 1,8 V (1,7 V til 1,9 V -rækkevidde), hvilket hjælper med at reducere strømforbruget sammenlignet med ældre 5 V CPLD'er.Denne lavere spænding er nyttig i moderne blandet spændingsspændings digitale systemer.

• Multi-spænding I/O-support

I/O -bankerne understøtter flere spændingsstandarder inklusive 1,5 V, 1,8 V, 2,5 V og 3,3 V. Denne fleksibilitet gør det muligt for CPLD at direkte interface med komponenter, der opererer ved forskellige spændingsniveauer uden skiftere på eksterne niveau.

• Højhastighedsoperation

Med en typisk forsinkelse af pin-to-pin-forplantning på ca. 5,7 ns (hastighedskvalitet "-7") leverer enheden hurtig, deterministisk ydelse.Dette gør det velegnet til timing-kritiske applikationer såsom adresseafkodning, bus voldgift og kontrol.

• Lavt strømforbrug

Coolrunner-II-serien er kendt for ekstremt lave standbystrømme, ofte i mikroampområdet.Denne lave statiske effekt kombineret med dynamiske effektbesparende funktioner tillader XC2C256-7TQ144C at blive brugt effektivt i batteridrevne eller altid-on-systemer.

• Datagate -teknologi

Denne funktion gør det muligt at gate ubrugte input, hvilket forhindrer unødvendig skiftende og reducerer dynamisk strømforbrug.Det er værdifuldt i applikationer, hvor visse signaler er inaktive i lange perioder.

• In-system JTAG-programmering

Enheden understøtter IEEE 1149.1 (JTAG) og IEEE 1532 til programmering i systemet.Dette betyder, at CPLD kan konfigureres, testes og omprogrammeres uden at fjerne det fra bestyrelsen, forenkle udvikling og opdateringer.

• Avanceret urstruktur

XC2C256-7TQ144C inkluderer flere globale ure, urdelere og dual-kant udløste registre.Det giver også globalt sæt/nulstilling og lokal ur per makrocell, hvilket giver fleksibel kontrol over timing og synkronisering.

• Schmitt-Trigger-input

Udvalgte inputstifter kan konfigureres, da Schmitt udløser til at forbedre støjimmuniteten.Dette er nyttigt til håndtering af langsomme eller støjende indgangssignaler uden at tilføje eksterne konditioneringskredsløb.

• Fleksible outputfunktioner

Outputs understøtter tre-statsoperation, dræbningsrentekontrol, bus-hold, åben drænkonfigurationer og valgfri pull-ups.Disse indstillinger gør det nemt at tilpasse CPLD til forskellige busstandarder og eksterne belastningsforhold.

• Avanceret Interconnect Matrix (AIM)

En avanceret sammenkoblingsmatrix forbinder effektivt funktionsblokke, der giver fuld produkt-term routing på tværs af enheden.Dette forbedrer den logiske placeringsfleksibilitet og hjælper med at opretholde forudsigelig timingydelse.

Coolrunner-II CPLD Arkitektur

Coolrunner-II CPLD-arkitekturen af XC2C256-7TQ144C er bygget omkring funktionsblokke, I/O-blokke og en avanceret sammenkoblingsmatrix (AIM).Hver funktionsblok indeholder makroceller og en programmerbar logikarray (PLA), der implementerer brugerdefineret logik, mens målet effektivt ruter signaler mellem blokke.I/O-blokke interface den interne logik med eksterne stifter og dedikeret JTAG og BSC/ISP-kredsløb support i systemet programmering og test.Denne strukturerede og sammenkoblede arkitektur muliggør hurtig, deterministisk ydelse med lavt strømforbrug, hvilket gør det ideelt til kontrol, grænseflade og limlogik i digitale systemer.

Typisk I/V -kurve for XC2C256

Den typiske I/V-kurve for XC2C256-7TQ144C illustrerer forholdet mellem udgangsspænding (VO) og udgangsstrøm (IO) for forskellige I/O-forsyningsspændinger (1,5 V, 1,8 V, 2,5 V og 3,3 V).Når forsyningsspændingen øges, kan enheden købe eller synke højere strømme, før udgangsspændingen begynder at falde markant.Denne opførsel er vigtig for at forstå CPLD's drivkapacitet, når det er interface med eksterne komponenter, hvilket sikrer, at signalniveauer forbliver gyldige under belastning.Mange bruger denne kurve til at vælge passende I/O-spændinger og sikre pålidelig drift i applikationer, der kræver specifikke aktuelle kørselsstyrker.

XC2C256-7TQ144C-specifikationer

|

Type |

Parameter |

|

Fabrikant |

AMD/Xilinx |

|

Serie |

Coolrunner II |

|

Emballage |

Bakke |

|

Delstatus |

Forældet |

|

Programmerbar type |

I systemprogrammerbar |

|

Forsinkelsestid TPD (1) Max |

6,7 ns |

|

Spændingsforsyning - intern |

1,7 V ~ 1,9 V |

|

Antal logiske elementer/blokke |

16 |

|

Antal makroceller |

256 |

|

Antal porte |

6000 |

|

Antal I/O. |

118 |

|

Driftstemperatur |

0 ° C ~ 70 ° C (TA) |

|

Monteringstype |

Overflademontering |

|

Pakke / sag |

144-LQFP

|

|

Leverandørenhedspakke |

144-TQFP (20 × 20) |

|

Basisproduktnummer |

XC2C256 |

XC2C256-7TQ144C applikationer

1. limlogik og interface brodannelse

XC2C256-7TQ144C er ideel til implementering af limlogik, der forbinder og koordinerer signaler mellem forskellige digitale komponenter.Det kan håndtere funktioner som adresseafkodning, bus voldgift og protokoloversættelse, hvilket muliggør jævn kommunikation mellem mikrokontrollere, hukommelse, sensorer og andre perifere enheder.Dens forudsigelige timing og hurtige pin-to-pin-forsinkelser sikrer pålidelig grænseflade, selv i komplekse brætdesign.

2. enheder med lav effekt og batteri

Takket være sin Fast Zero Power (FZP) -teknologi og meget lav standbystrøm er denne CPLD meget velegnet til bærbar og batteridrevet elektronik.Det kan forblive drevet kontinuerligt, mens den indtages minimal energi, hvilket gør den perfekt til altid kontrol eller overvågningskredsløb.Du kan reducere strømforbruget yderligere med funktioner som Datagate, hvilket minimerer dynamisk switching, når input er inaktive.

3. Kontrollogik og sekventering

Enheden udmærker sig ved implementering af endelige tilstandsmaskiner, timingkontrol og signalsekventering, der kræves i mange indlejrede systemer.Dens deterministiske, ikke-flygtige arkitektur gør det muligt for kontrollogikken at blive aktiv umiddelbart efter opstart uden konfigurationsforsinkelser.Dette gør det til et stærkt valg for nulstilling af logik, håndskivkredsløb og andre tidskritiske kontrolopgaver.

4. Indlejret systemstøtte og perifer logik

I indlejrede design kan XC2C256-7TQ144C fungere som en tilpasselig supportchip, implementere specialiserede grænseflader eller udvide en mikrokontrollers kapacitet.Det kan håndtere kommunikationsprotokoller som SPI, I²C eller UART, generere ChIP -valg eller administrere interrupt routing.Ved at aflaste disse funktioner fra CPU'en forenkler det firmwareudvikling og forbedrer den samlede systemydelse.

XC2C256-7TQ144C Lignende dele

|

Specifikation |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Enhedsfamilie |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

Coolrunner-ii cpld |

|

Logikdensitet (makroceller) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Pakningstype |

TQFP-144 |

TQFP-144 |

TQFP-144 (PB-fri) |

VQFP-100 |

VQFP-100 (PB-fri) |

TQFP-144 |

|

Hastighedskvalitet |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (hurtigere) |

|

Temperaturområde |

Kommerciel (0 - 70 ° C) |

Industriel (-40-85 ° C) |

Industriel (-40-85 ° C) |

Kommerciel (0 - 70 ° C) |

Kommerciel (0 - 70 ° C) |

Kommerciel (0 - 70 ° C) |

|

I/O -pin -tælling |

118 |

118 |

118 |

80 |

80 |

118 |

|

Core Voltage (VCC) |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

1,8 v |

|

I/O -spændingsstøtte |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

|

Overholdelse / PB-fri |

Standard |

Standard |

Pb-fri / Rohs |

Standard |

Pb-fri / Rohs |

Standard |

|

Forskelle |

Baseline kommerciel version |

Industriel temp -version |

Industriel + PB-fri version |

Mindre pakke, færre I/O |

PB-fri mindre version |

Hurtigere timing -version |

XC2C256-7TQ144C programmeringstrin

Programmering af XC2C256-7TQ144C er en ligetil proces, der involverer at forberede dit design, generere programmeringsfilen og indlæse den i CPLD gennem JTAG.Ved at følge hvert trin omhyggeligt kan du sikre en vellykket konfiguration og korrekt enhedsdrift på dit bord.

1. design og syntetiser

Du starter med at skrive dit logikdesign ved hjælp af HDL (VHDL eller Verilog) eller skematisk indrejse.Efter at have afsluttet designet kører du synteseprocessen, der konverterer din logik til enhedens interne struktur af makroceller og sammenkoblinger.Dette trin sikrer, at dit design er kompatibelt med XC2C256 -arkitekturen og klar til implementering.

2. sted & rute / implementering (montering)

Dernæst udfører du sted og rute, også kendt som montering, der tildeler din syntetiserede logik til faktiske fysiske makroceller og routingressourcer inde i CPLD.Værktøjet kontrollerer timingbegrænsninger, løser ressourceforbrug og optimerer stier til at imødekomme ydelsen af dit design.Dette sikrer, at kredsløbet kører pålideligt, når den er programmeret til enheden.

3. generere programmeringsfil

Når implementeringen er afsluttet, genererer du programmeringsfilen (BIT, JAM eller SVF -format), der indeholder de nøjagtige konfigurationsdata for enheden.Denne fil repræsenterer, hvordan hver makrocell, sammenkobling og I/O er indstillet til at implementere din logik.At have denne fil klar er nødvendig, inden du går videre til den faktiske enhedsprogrammering.

4. JTAG / In-system-programmering

Endelig forbinder du enheden til din pc ved hjælp af et JTAG -programmeringskabel og åbner Xilinx Impact Tool (eller tilsvarende).Derefter indlæser du den genererede programmeringsfil og downloader den til XC2C256-7TQ144C gennem JTAG-stifterne (TDI, TDO, TCK, TMS).Når processen er afsluttet, begynder CPLD straks at arbejde med din programmerede logik uden at kræve en strømcyklus eller ekstern konfigurationshukommelse.

XC2C256-7TQ144C fordele og ulemper

Fordele

• Meget lav standby-strøm, ideel til batteridrevet design.

• Øjeblikkelig drift uden konfigurationsforsinkelse.

• Forudsigelig timing for lettere designlukning.

• Erstatter flere diskrete logiske chips, sparer plads og omkostninger.

• Understøtter flere I/O -spændinger uden skift på eksterne niveau.

Ulemper

• Begrænset logikkapacitet sammenlignet med større CPLD'er eller FPGA'er.

• Ingen indbygget DSP, RAM eller højhastighedstransceivere.

• At blive forældet og gøre fremtidig indkøb hårdere.

• Lavere ydelsesloft til applikationer med høj hastighed.

• Mindre routingfleksibilitet for komplekse eller uregelmæssige design.

XC2C256-7TQ144C Emballagedimensioner

|

Type |

Parameter |

|

Pakningstype |

TQFP-144 |

|

Pakke kropsstørrelse |

20 mm × 20 mm |

|

Bly tonehøjde |

0,5 mm |

|

Antal stifter |

144 |

|

Pakkehøjde (max) |

1,4 mm |

|

Pakningstykkelse (nominel) |

1,0 mm |

|

Blylængde |

0,45 mm ~ 0,75 mm |

|

Ledbredde |

0,17 mm ~ 0,27 mm |

|

Monteringstype |

Overflademontering |

|

Leverandørenhedspakke |

144-TQFP (20 × 20) |

XC2C256-7TQ144C Producent

XC2C256-7TQ144C er fremstillet af Xilinx, et førende firma i programmerbare logiske løsninger.Xilinx er bredt anerkendt for banebrydende FPGA- og CPLD-teknologier, der leverer pålidelige og højtydende enheder til industrielle, kommercielle og forbrugerapplikationer.I dag fungerer Xilinx som en del af AMD, fortsætter med at levere avancerede programmerbare logikprodukter med stærk langvarig support og innovation.

Konklusion

XC2C256-7TQ144C skiller sig ud for sit lave strømforbrug, hurtig deterministisk ydelse og multi-spænding I/O-fleksibilitet, hvilket gør det til et pålideligt valg til moderne digitale design.Dens afbalancerede kombination af 256 makroceller, 118 I/O -stifter og avanceret interconnect -arkitektur understøtter en lang række kontrol-, grænseflade- og limlogikfunktioner.Med support til programmering i systemet, datagat-strømbesparende funktioner og robuste I/O-konfigurationer, integreres det glat i indlejrede systemer og blandede spændingsmiljøer.

Datablad PDF

XC2C256-7TQ144C Datablad:

Om os

ALLELCO LIMITED

Læs mere

Hurtig forespørgsel

Send en forespørgsel, vi svarer med det samme.

Ofte stillede spørgsmål [FAQ]

1. Kræver XC2C256-7TQ144C ekstern konfigurationshukommelse?

Nej. En af dens fordele er øjeblikkelig drift.Konfigurationen gemmes internt, så den driver klar til at køre uden nogen ekstern prom eller flashhukommelse.

2. Hvilke programmeringsværktøjer er kompatible med XC2C256-7TQ144C?

Du kan programmere enheden ved hjælp af Xilinx Impact -software med et JTAG -programmeringskabel.Mange bruger også kompatible tredjeparts JTAG-programmerere, men sørg for, at de understøtter IEEE 1149.1/1532 standarder.

3. kan XC2C256-7TQ144C erstatte flere diskrete logik ics i dit design?

Ja.Med sine 256 makroceller og fleksible I/O, kan denne CPLD integrere flere limlogik- og kontrolfunktioner i en enhed, hvilket hjælper dig med at reducere bestyrelsesrum og komponentantal.

4. er XC2C256-7TQ144C velegnet til batteri-applikationer med lav effekt?

Ja.Takket være sin Fast Zero Power (FZP) -teknologi og meget lav standbystrøm er den ideel til altid-on-kredsløb, bærbare enheder og strømfølsomme indlejrede systemer.

5. Kan du bruge XC2C256-7TQ144C til højhastighedssignalbehandling?

Det er ikke designet til højhastigheds DSP- eller transceiveropgaver.Mens det leverer hurtige pin-to-pin-forsinkelser, er det bedst egnet til kontrol, grænseflade og timing-logik, ikke kompleks databehandling.

EP2S60F672C4 FPGA: Funktioner, applikationer, programmering og databladsvejledning

på 2025-10-04

EPM3256AFC256-7 CPLD Oversigt: Funktioner, pinout, programmering og applikationer

på 2025-10-03

Populære indlæg

-

Kompleks instruktionssæt computere: Hvordan de ændrede computing?

på 8000-04-18 147778

-

USB-C pinout og funktioner

på 2000-04-18 112036

-

Brug af Xilinx Unified Simulering Primitiver: En omfattende guide til FPGA -design og simulering

på 1600-04-18 111352

-

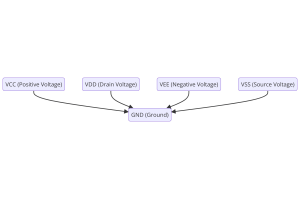

Strømforsyningsspændinger i elektronik: Betydning af VCC, VDD, VEE, VSS og GND

på 0400-04-18 83794

-

RJ45 Connector Guide: Pinout, ledninger, kabeltyper og anvendelser

på 1970-01-01 79602

-

Den ultimative guide til trådfarvekoder i moderne elektriske systemer

Den måde, vores elektriske systemer bruger farver på, er ikke kun til udseende.Hver trådfarve angiver nu en bestemt funktion, hvilket gør det lettere at identificere og håndtere elektriske komponen...på 1970-01-01 66978

-

Purge Valve Guide: Funktion, symptomer, test og udskiftning for optimal motorydelse

Purge -ventilen er en vigtig del af en bils system, der hjælper med at holde luften ren ved at håndtere brændstofdampe, før de kan flygte ud i atmosfæren.Dette hjælper ikke kun miljøet ved at reduc...på 1970-01-01 63111

-

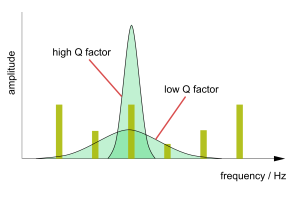

Kvalitet (q) Faktor: Ligninger og applikationer

Kvalitetsfaktoren eller 'Q' er vigtig, når man kontrollerer, hvor godt induktorer og resonatorer fungerer i elektroniske systemer, der bruger radiofrekvenser (RF).'Q' måler, hvor godt et kredsløb m...på 1970-01-01 63044

-

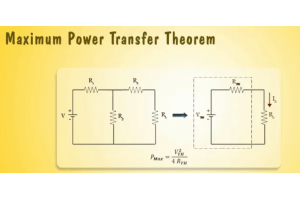

Opnå spidsydelse med den maksimale effektoverførselsteorem

Den maksimale effektoverførselssætning forklarer, hvordan energi fra en kilde, såsom et batteri eller generator, flyder til en tilsluttet belastning.Det viser den nøjagtige betingelse, hvor belastn...på 1970-01-01 54097

-

A23 batterispecifikationer og kompatibilitet

A23-batteriet er et lille, cylinderformet batteri med høj spænding.Også kaldet 23A, 23AE eller MN21 kører den på 12 volt og meget højere end AA- eller AAA -batterier.Dets specielle design ...på 1970-01-01 52198